User’s Manual

Preliminary PPC440x5 CPU Core

prgmodel.fm.

September 12, 2002

Page 81 of 589

2.8.2 Privileged SPRs

Most SPRs are privileged. The only defined non-privileged SPRs are the LR, CTR, XER, USPRG0, SPRG4–

7 (read access only), TBU (read access only), and TBL (read access only). The PPC440x5 core also treats

all SPR numbers with a 1 in bit 5 of the SPRN field as privileged, whether the particular SPR number is

defined or not. Thus the core causes a Privileged Instruction exception type Program interrupt on any attempt

to access such an SPR number while in user mode. In addition, the core causes an Illegal Instruction excep-

tion type Program interrupt on any attempt to access while in user mode an undefined SPR number with a 0

in SPRN

5

. On the other hand, the result of attempting to access an undefined SPR number in supervisor

mode is undefined, regardless of the value in SPRN

5

.

2.9 Speculative Accesses

The PowerPC Book-E Architecture permits implementations to perform speculative accesses to memory,

either for instruction fetching, or for data loads. A speculative access is defined as any access that is not

required by the sequential execution model (SEM).

For example, the PPC440x5 speculatively prefetches instructions down the predicted path of a conditional

branch; if the branch is later determined to not go in the predicted direction, the fetching of the instructions

from the predicted path is not required by the SEM and thus is speculative. Similarly, the PPC440x5 executes

load instructions out-of-order, and may read data from memory for a load instruction that is past an undeter-

mined branch.

Sometimes speculative accesses are inappropriate, however. For example, attempting to access data at

addresses to which I/O devices are mapped can cause problems. If the I/O device is a serial port, reading it

speculatively could cause data to be lost.

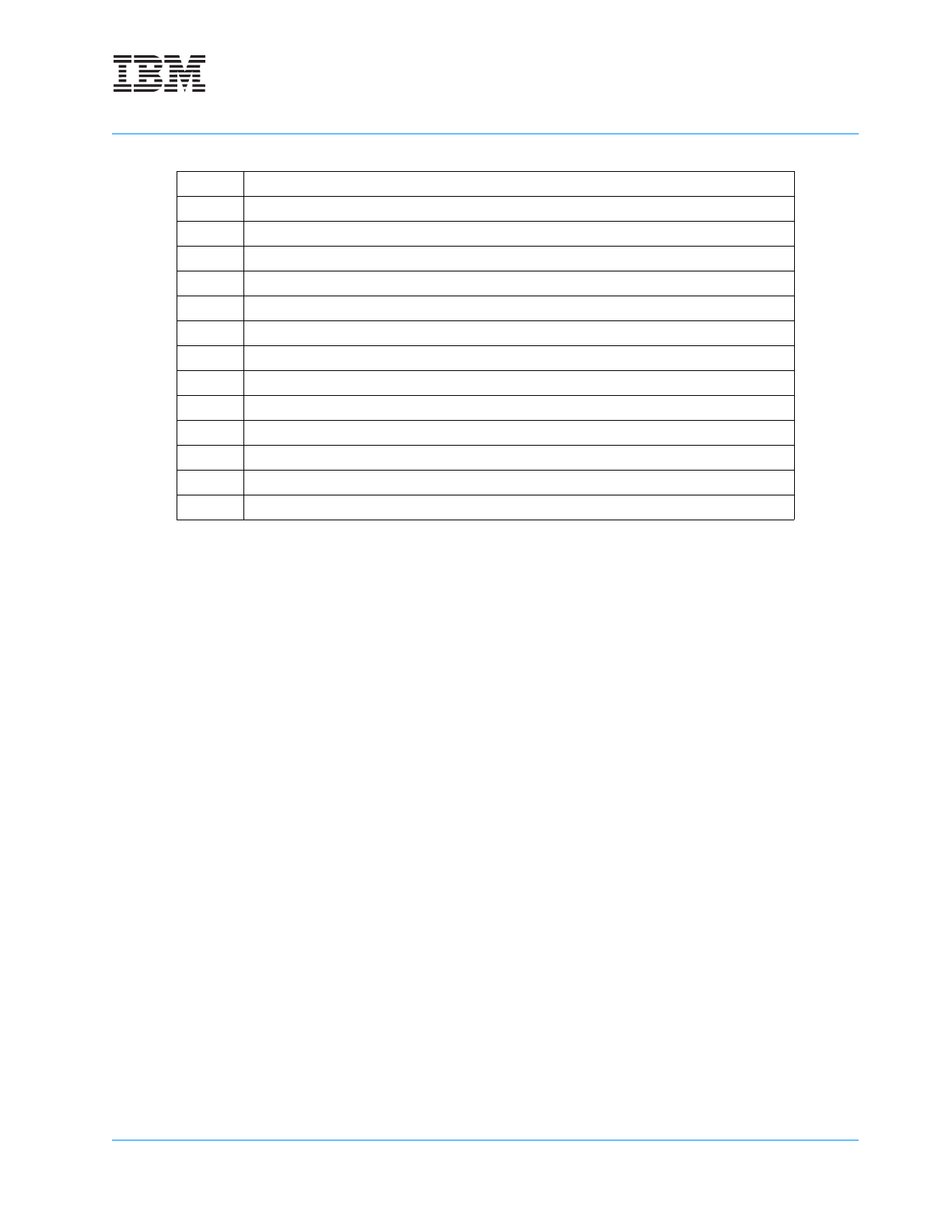

mfmsr

mfspr

For any SPR Number with SPRN

5

= 1. See Privileged SPRs on page 81.

mtdcr

mtmsr

mtspr

For any SPR Number with SPRN

5

= 1. See Privileged SPRs on page 81.

rfci

rfi

rfmci

tlbre

tlbsx

tlbsync

tlbwe

wrtee

wrteei

Table 2-27. Privileged Instructions (continued)