User’s Manual

PPC440x5 CPU Core Preliminary

Page 98 of 589

cache.fm.

September 12, 2002

The size of the victim index fields varies according to the size of the respective cache. Also, which field is

used varies according to the type of access, the size of the cache, and the address of the cache line.

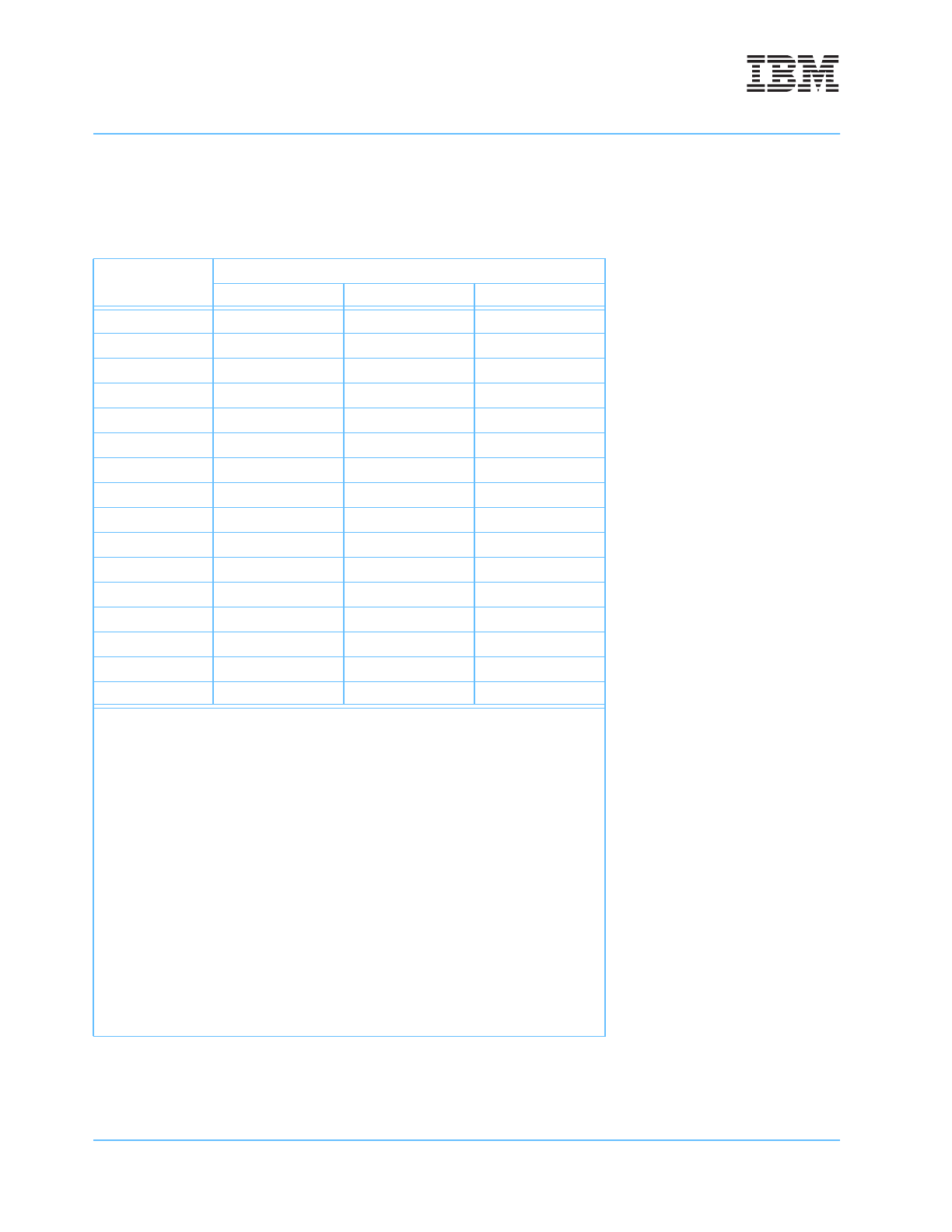

Table 4-3 describes the correlation between the victim index fields and different access types, cache sizes,

and addresses.

Table 4-3. Victim Index Field Selection

Address

23:26

3

Victim Index Field

1,2

8KB Cache 16KB Cache 32KB Cache

0 xxV0[VNDXA]

3:7

xxV0[VNDXA]

2:7

xxV0[VNDXA]

2:7

1 xxV0[VNDXB]

3:7

xxV0[VNDXB]

2:7

xxV0[VNDXB]

2:7

2 xxV0[VNDXC]

3:7

xxV0[VNDXC]

2:7

xxV0[VNDXC]

2:7

3 xxV0[VNDXD]

3:7

xxV0[VNDXD]

2:7

xxV0[VNDXD]

2:7

4 xxV1[VNDXA]

3:7

xxV1[VNDXA]

2:7

xxV1[VNDXA]

2:7

5 xxV1[VNDXB]

3:7

xxV1[VNDXB]

2:7

xxV1[VNDXB]

2:7

6 xxV1[VNDXC]

3:7

xxV1[VNDXC]

2:7

xxV1[VNDXC]

2:7

7 xxV1[VNDXD]

3:7

xxV1[VNDXD]

2:7

xxV1[VNDXD]

2:7

8 xxV0[VNDXA]

3:7

xxV0[VNDXA]

2:7

xxV2[VNDXA]

2:7

9 xxV0[VNDXB]

3:7

xxV0[VNDXB]

2:7

xxV2[VNDXB]

2:7

10 xxV0[VNDXC]

3:7

xxV0[VNDXC]

2:7

xxV2[VNDXC]

2:7

11 xxV0[VNDXD]

3:7

xxV0[VNDXD]

2:7

xxV2[VNDXD]

2:7

12 xxV1[VNDXA]

3:7

xxV1[VNDXA]

2:7

xxV3[VNDXA]

2:7

13 xxV1[VNDXB]

3:7

xxV1[VNDXB]

2:7

xxV3[VNDXB]

2:7

14 xxV1[VNDXC]

3:7

xxV1[VNDXC]

2:7

xxV3[VNDXC]

2:7

15 xxV1[VNDXD]

3:7

xxV1[VNDXD]

2:7

xxV3[VNDXD]

2:7

Note 1: In the victim index field columns, the “xx” in the SPR name refers

to one of “IN”, “IT”, “DN”, or “DT”, depending on whether the

access is to the instruction or data cache, and whether it is a

“normal” or a “transient” access (See Cache Locking and

Transient Mechanism on page 99.)

Note 2: As shown in the table, the 8KB cache size only uses bits 3:7 of

the victim index fields to select a way, since there are only 32

ways. Similarly, the 16KB and 32KB cache sizes uses bits 2:7 of

the victim index fields, since those cache sizes have 64 ways. In

all cases, the unused bits of the victim index fields are reserved.

The size of the fields of the victim limit registers (IVLIM, DVLIM)

are similarly affected by the number of sets in the cache (See

Cache Locking and Transient Mechanism on page 99.)

Note 3: Since the 8KB and 16KB cache sizes only have 8 sets, they only

use Address

24:26

to select the set and the victim index field, and

thus they do not use the xxV2 and xxV3 SPRs.