User’s Manual

Preliminary PPC440x5 CPU Core

debug.fm.

September 12, 2002

Page 245 of 589

8.6.5 Instruction Address Compare Registers (IAC1–IAC4)

The four IAC registers specify the addresses upon which IAC debug events should occur. Each of the IAC

registers can be written from a GPR using mtspr, and can be read into a GPR using mfspr.

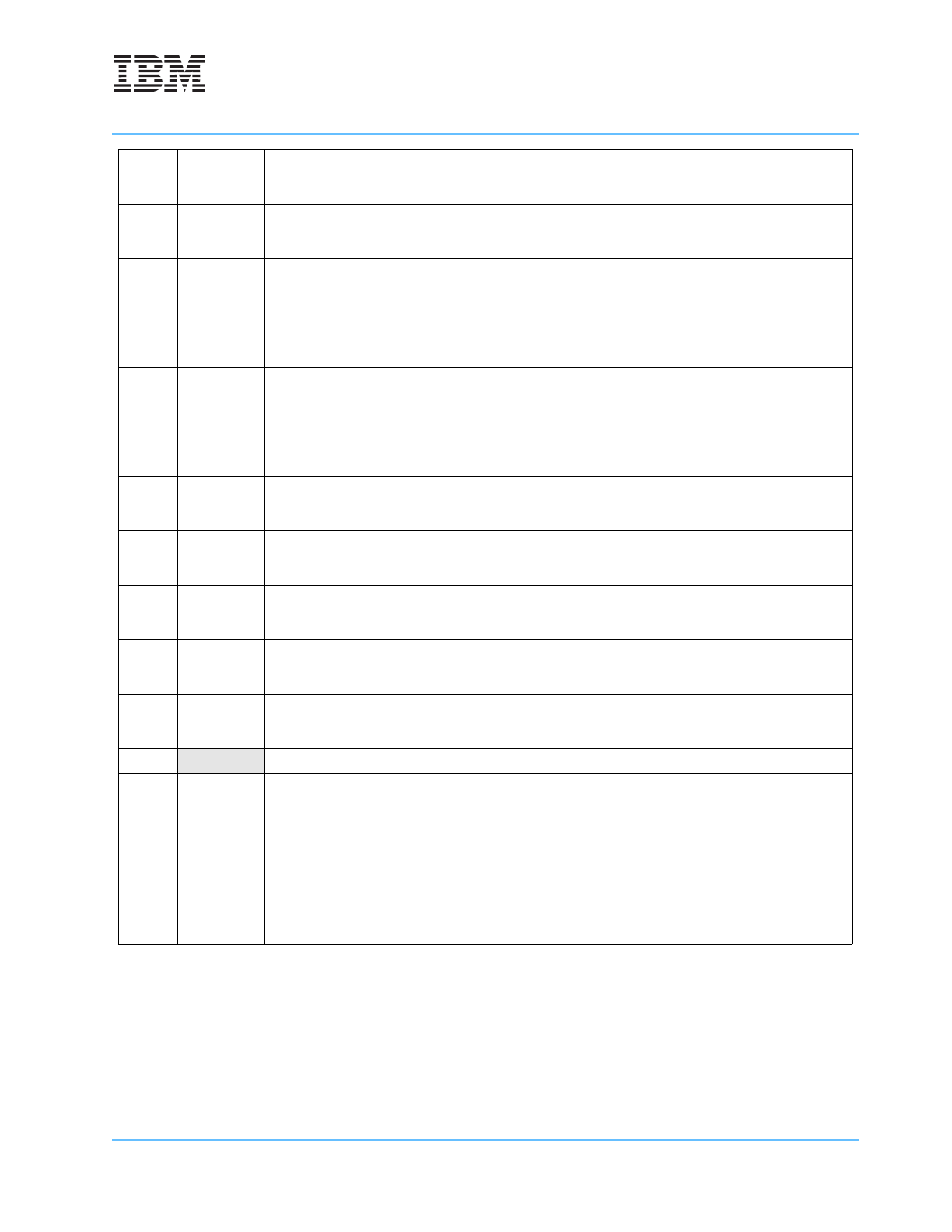

6 IRPT

Interrupt Debug Event

0 Event didn’t occur

1 Event occurred

7 TRAP

Trap Debug Event

0 Event didn’t occur

1 Event occurred

8 IAC1

IAC 1 Debug Event

0 Event didn’t occur

1 Event occurred

9 IAC2

IAC 2 Debug Event

0 Event didn’t occur

1 Event occurred

10 IAC3

IAC 3 Debug Event

0 Event didn’t occur

1 Event occurred

11 IAC4

IAC 4 Debug Event

0 Event didn’t occur

1 Event occurred

12 DAC1R

DAC 1 Read Debug Event

0 Event didn’t occur

1 Event occurred

13 DAC1W

DAC 1 Write Debug Event

0 Event didn’t occur

1 Event occurred

14 DAC2R

DAC 2 Read Debug Event

0 Event didn’t occur

1 Event occurred

15 DAC2W

DAC 2 Write Debug Event

0 Event didn’t occur

1 Event occurred

16 RET

Return Debug Event

0 Event didn’t occur

1 Event occurred

17:29 Reserved

30 IAC12ATS

IAC 1/2 Auto-Toggle Status

0 Range is not reversed from value specified in

DBCR1[IAC12M]

1 Range is reversed from value specified in

DBCR1[IAC12M]

31 IAC34ATS

IAC 3/4 Auto-Toggle Status

0 Range is not reversed from value specified in

DBCR1[IAC34M]

1 Range is reversed from value specified in

DBCR1[IAC34M]