User’s Manual

Preliminary PPC440x5 CPU Core

prgmodel.fm.

September 12, 2002

Page 63 of 589

2.4.4.3 Storage Synchronization Instructions

The storage synchronization instructions allow software to enforce ordering amongst the storage accesses

caused by load and store instructions, which by default are “weakly-ordered” by the processor. “Weakly-

ordered” means that the processor is architecturally permitted to perform loads and stores generally out-of-

order with respect to their sequence within the instruction stream, with some exceptions. However, if a

storage synchronization instruction is executed, then all storage accesses prompted by instructions

preceding the synchronizing instruction must be performed before any storage accesses prompted by

instructions which come after the synchronizing instruction. See Synchronization on page 82 for more infor-

mation on storage synchronization.

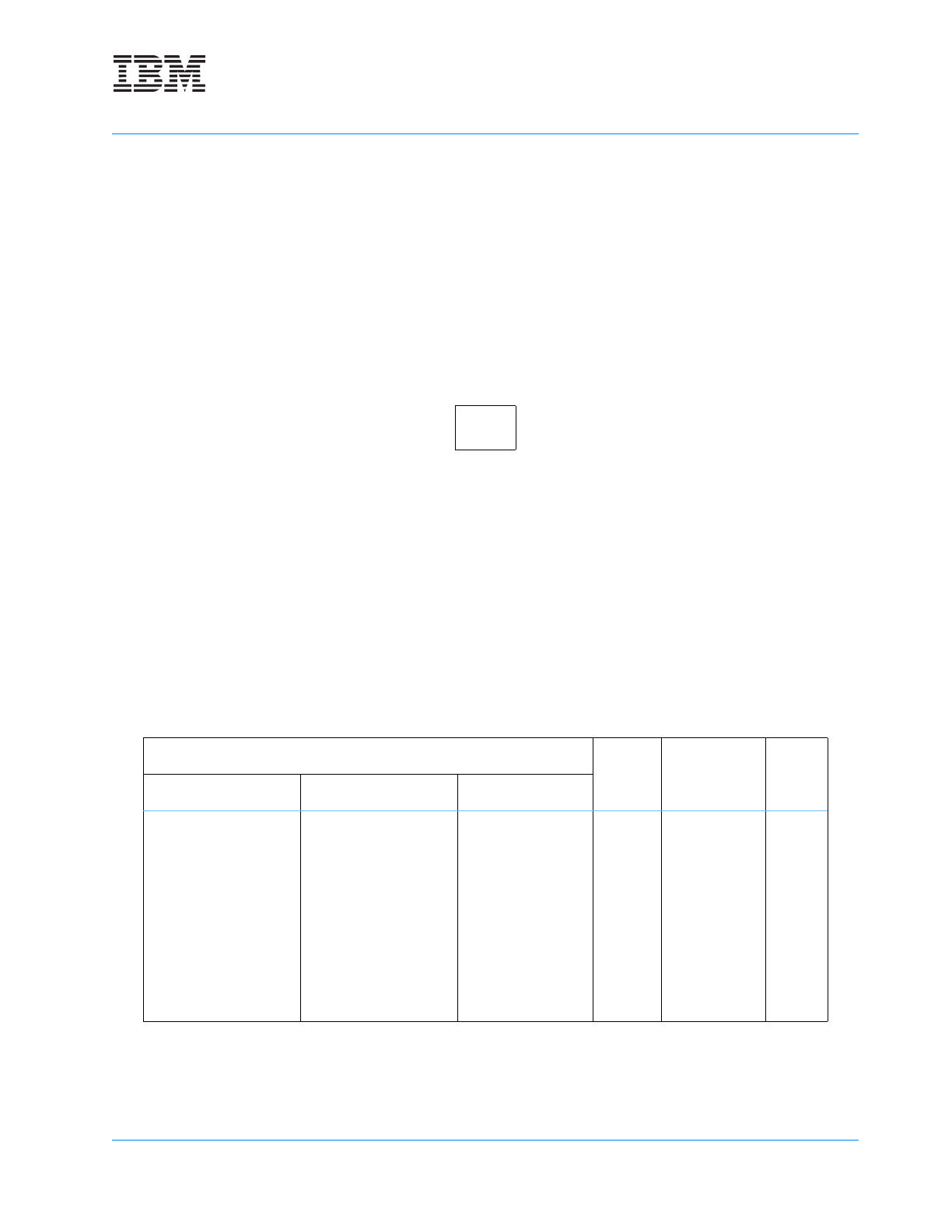

Table 2-17 shows the storage synchronization instructions in the PPC440x5.

2.4.5 Allocated Instructions

These instructions are not part of the PowerPC Book-E architecture, but they are included as part of the

PPC440x5 core. Architecturally, they are considered allocated instructions, as they use opcodes which are

within the allocated class of instructions, which the PowerPC Book-E architecture identifies as being available

for implementation-dependent and/or application-specific purposes. However, all of the allocated instructions

which are implemented within the PPC440x5 core are “standard” for IBM’s family of PowerPC embedded

controllers, and are not unique to the PPC440x5.

The allocated instructions implemented within the PPC440x5 are divided into four sub-categories, and are

shown in Table 2-21. See Integer Arithmetic Instructions on page 58 for an explanation of the “[.]” and “[o]”

syntax.

Table 2-20. Storage Synchronization Instructions

msync

mbar

Table 2-21. Allocated Instructions

Arithmetic Logical

Cache

Management

Cache

Debug

Multiply-Accumulate

Negative

Multiply-Accumulate

Multiply Halfword

macchw[o][.]

macchws[o][.]

macchwsu[o][.]

macchwu[o][.]

machhw[o][.]

machhws[o][.]

machhwsu[o][.]

machhwu[o][.]

maclhw[o][.]

maclhws[o][.]

maclhwsu[o][.]

maclhwu[o][.]

nmacchw[o][.]

nmacchws[o][.]

nmachhw[o][.]

nmachhws[o][.]

nmaclhw[o][.]

nmaclhws[o][.]

mulchw[.]

mulchwu[.]

mulhhw[.]

mulhhwu[.]

mullhw[.]

mullhwu[.]

dlmzb[.]

dccci

iccci

dcread

icread