User’s Manual

PPC440x5 CPU Core Preliminary

Page 244 of 589

debug.fm.

September 12, 2002

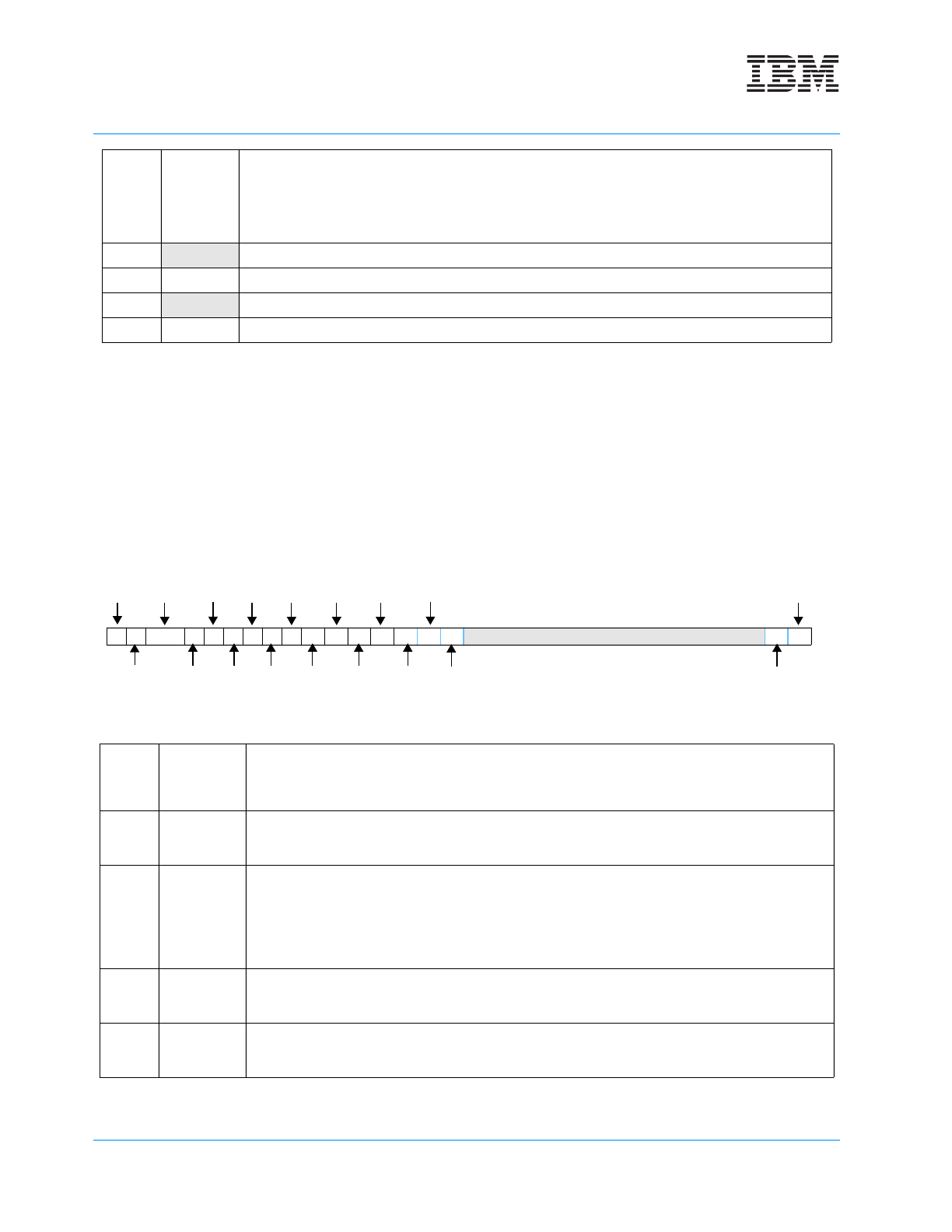

8.6.4 Debug Status Register (DBSR)

The DBSR contains status on debug events as well as information on the type of the most recent reset. The

status bits are set by the occurrence of debug events, while the reset type information is updated upon the

occurrence of any of the three reset types.

The DBSR is read into a GPR using mfspr. Clearing the DBSR is performed using mtspr by placing a 1 in

the GPR source register in all bit positions which are to be cleared in the DBSR, and a 0 in all other bit posi-

tions. The data written from the GPR to the DBSR is not direct data, but a mask. A 1 clears the bit and a 0

leaves the corresponding DBSR bit unchanged.

14:15 DVC2M

DVC 2 Mode

00 Reserved

01 AND all bytes enabled by DVC2BE

10 OR all bytes enabled by DVC2BE

11 AND-OR pairs of bytes enabled by DVC2BE

(0 AND 1) OR (2 AND 3)

16:19

Reserved

20:23 DVC1BE DVC 1 Byte Enables 0:3

24:27 Reserved

28:31 DVC2BE DVC 2 Byte Enables 0:3

Figure 8-4. Debug Status Register (DBSR)

0 IDE

Imprecise Debug Event

0 Debug event ocurred while MSR[DE] = 1

1 Debug event occurred while MSR[DE] = 0

For synchronous debug events in internal debug

mode, this field indicates whether the correspond-

ing Debug interrupt occurs precisely or impre-

cisely

1 UDE

Unconditional Debug Event

0 Event didn’t occur

1 Event occurred

2:3 MRR

Most Recent Reset

00 No reset has occurred since this field was last

cleared by software.

01 Core reset

10 Chip reset

11 System reset

This field is set upon any processor reset to a

value indicating the type of reset.

4 ICMP

Instruction Completion Debug Event

0 Event didn’t occur

1 Event occurred

5 BRT

Branch Taken Debug Event

0 Event didn’t occur

1 Event occurred

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 29 30 31

IDE

UDE ICMP IRPT IAC1

MRR

BRT

IAC2

DAC2W

DAC1R

TRAP

IAC3

IAC4

DAC1W

DAC2R

IAC12ATS

IAC34AT

S

RET