User’s Manual

PPC440x5 CPU Core Preliminary

Page 76 of 589

prgmodel.fm.

September 12, 2002

2.7.3 Processor Identification Register (PIR)

The PIR is a read-only register that uniquely identifies a specific instance of a processor core, within a multi-

processor configuration, enabling software to determine exactly which processor it is running on. This capa-

bility is important for operating system software within multiprocessor configurations. The PIR can be read

into a GPR using mfspr.

Because the PPC440x5 is a uniprocessor, PIR[PIN] = 0b0000.

Access to the PIR is privileged.

2.7.4 Core Configuration Register 0 (CCR0)

The CCR0 controls a number of special chip functions, including data cache and auxiliary processor opera-

tion, speculative instruction fetching, trace, and the operation of the cache block touch instructions. The

CCR0 is written from a GPR using mtspr, and can be read into a GPR using mfspr. Figure 2-11 on page 77

illustrates the fields of the CCR0, and gives a brief description of their functions. A cross reference after the

bit-field description indicates the section of this document which describes each field in more detail.

Access to the CCR0 is privileged.

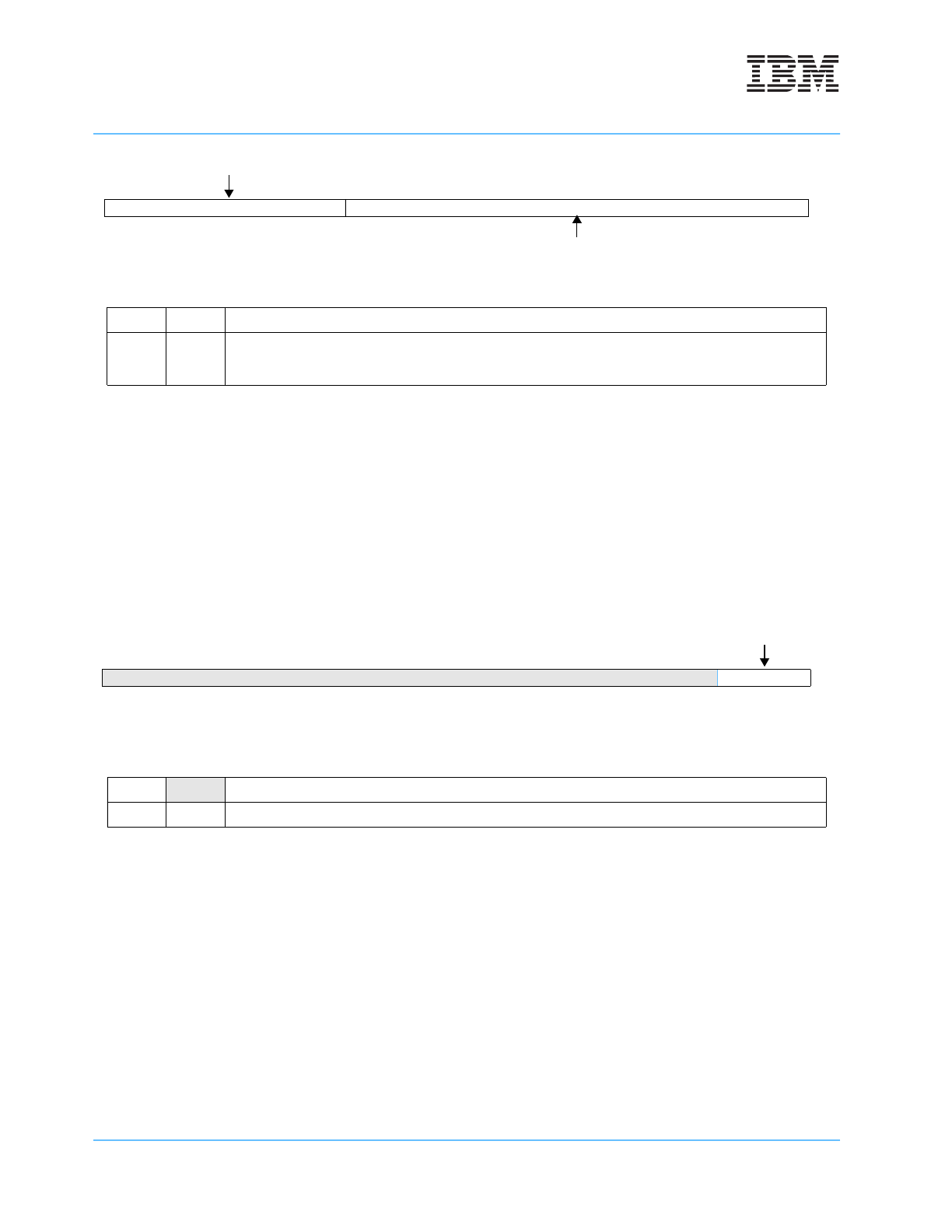

Figure 2-9. Processor Version Register (PVR)

0:11 OWN Owner Identifier Identifies the owner of a core.

12:31 PVN Processor Version Number

Implementation-specific value identifying the spe-

cific version and use of a processor core within a

chip.

Figure 2-10. Processor Identification Register (PIR)

0:27 Reserved

28:31 PIN Processor Identification Number (PIN)

01112 31

PVN

OWN

0 27 28 31

PIN