User’s Manual

PPC440x5 CPU Core Preliminary

Page 112 of 589

cache.fm.

September 12, 2002

When being used for these latter purposes, it is important that the icbt instruction deliver a deterministic

result, namely the guaranteed establishment in the cache of the specified line. Accordingly, the PPC440x5

core provides a field in the CCR0 register that can be used to cause the icbt instruction to operate in this

manner. Specifically, when the CCR0 [GICBT] field is set, the execution of icbt is guaranteed to establish the

specified cache line in the instruction cache (assuming that a TLB entry for the referenced memory page

exists and has both read and execute permission, and that the caching inhibited storage attribute is not set).

The cache line fill associated with such a guaranteed icbt will not be abandoned due to subsequent instruc-

tion cache misses.

Operation of the

icbt instruction is affected by the CCR1[FCOM] bit, which forces the icbt to appear to miss

the cache, even if it should really be a hit. This causes two copies of the line to be established in the cache,

simulating a multi-hit parity error. See section 4.2.4.7, “Simulating Instruction Cache Parity Errors for Soft-

ware Testing.”

4.2.4.5 icread Operation

The icread instruction can be used to directly read both the tag and instruction information of a specified

word in a specified entry of the instruction cache. The instruction information is read into the Instruction

Cache Debug Data Register (ICDBDR), while the tag information is read into a pair of SPRs, the Instruction

Cache Debug Tag Register High (ICDBTRH) and Instruction Cache Debug Tag Register Low (ICDBTRL).

From there, the information can subsequently be moved into GPRs using mfspr instructions.

The execution of the icread instruction generates the equivalent of an EA, which is then broken down

according to the size of the cache and used to select a specific instruction word from a specific cache line, as

shown in Table 4-4:

The EA generated by the icread instruction must be word-aligned (that is, EA

30:31

must be 0); otherwise, it is

a programming error and the result is undefined.

If the CCR0[CRPE] bit is set, execution of the icread instruction also loads parity information into the

ICBDTRH.

Execution of the icread instruction is privileged, and is intended for use for debugging purposes only.

Programming Note:

The PPC440x5 does not automatically synchronize context between an icread instruction and

the subsequent mfspr instructions which read the results of the icread instruction into GPRs. In

order to guarantee that the mfspr instructions obtain the results of the icread instruction, a

sequence such as the following must be used:

icread regA,regB # read cache information (the contents of GPR A and GPR B are

# added and the result used to specify a cache line index to be read)

isync # ensure icread completes before attempting to read results

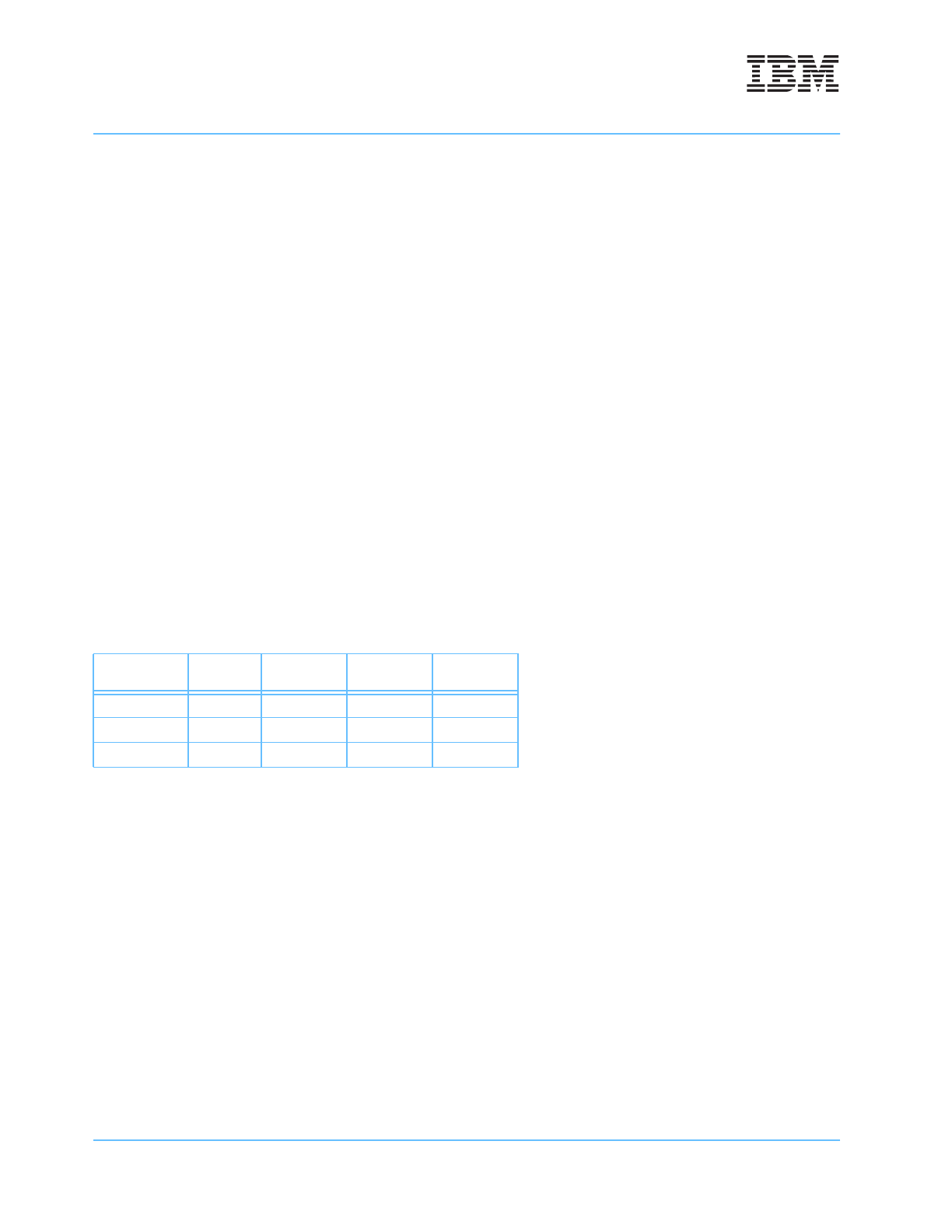

Table 4-4. Icread and dcread Cache Line Selection

Array Size Ignored

Way

Selection

Set

Selection

Word

Selection

8KB EA

0:18

EA

19:23

EA

24:26

EA

27:29

16KB EA

0:17

EA

18:23

EA

24:26

EA

27:29

32KB EA

0:16

EA

17:22

EA

23:26

EA

27:29