User’s Manual

PPC440x5 CPU Core Preliminary

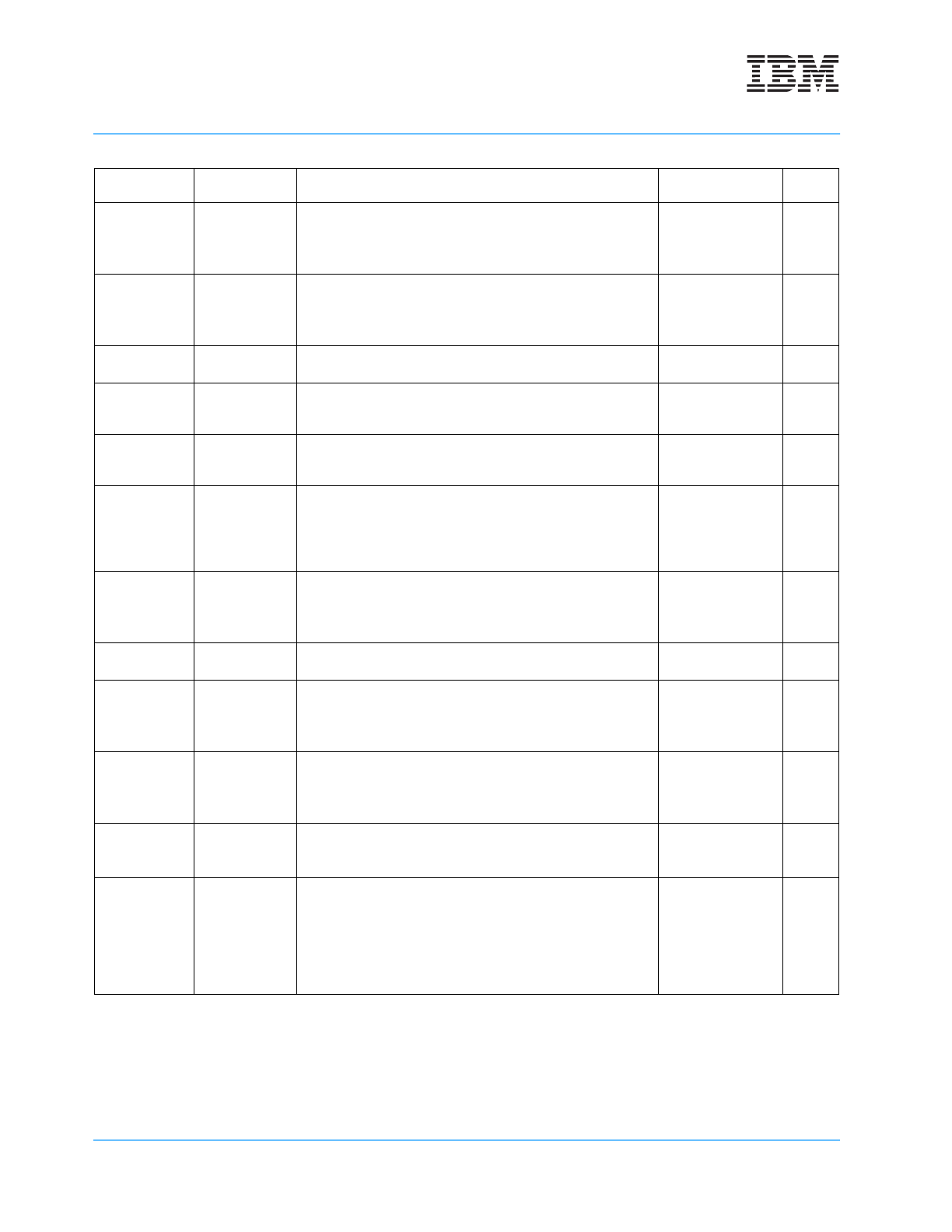

Page 540 of 589

instalfa.fm.

September 12, 2002

lhau

RT, D(RA)

Load halfword from EA = (RA|0) + EXTS(D) and sign extend,

(RT) ← EXTS(MS(EA,2)).

Update the base address,

(RA) ← EA.

326

lhaux

RT, RA, RB

Load halfword from EA = (RA|0) + (RB) and sign extend,

(RT) ← EXTS(MS(EA,2)).

Update the base address,

(RA) ← EA.

327

lhax

RT, RA, RB

Load halfword from EA = (RA|0) + (RB) and sign extend,

(RT) ← EXTS(MS(EA,2)).

328

lhbrx

RT, RA, RB

Load halfword from EA = (RA|0) + (RB), then reverse byte order

and pad left with zeroes,

(RT) ←

16

0 || MS(EA+1,1) || MS(EA,1).

329

lhz

RT, D(RA)

Load halfword from EA = (RA|0) + EXTS(D) and pad left with

zeroes,

(RT) ←

16

0 || MS(EA,2).

330

lhzu

RT, D(RA)

Load halfword from EA = (RA|0) + EXTS(D) and pad left with

zeroes,

(RT) ←

16

0 || MS(EA,2).

Update the base address,

(RA) ← EA.

331

lhzux

RT, RA, RB

Load halfword from EA = (RA|0) + (RB) and pad left with zeroes,

(RT) ←

16

0 || MS(EA,2).

Update the base address,

(RA) ← EA.

332

lhzx

RT, RA, RB

Load halfword from EA = (RA|0) + (RB) and pad left with zeroes,

(RT) ←

16

0 || MS(EA,2).

333

li

RT, IM

Load immediate.

(RT) ← EXTS(IM)

Extended mnemonic for

addi RT,0,value

258

lis

RT, IM

Load immediate shifted.

(RT) ← (IM ||

16

0)

Extended mnemonic for

addis RT,0,value

261

lmw

RT, D(RA)

Load multiple words starting from EA = (RA|0) + EXTS(D).

Place into consecutive registers RT through GPR(31).

RA is not altered unless RA = GPR(31).

334

lswi

RT, RA, NB

Load consecutive bytes from EA=(RA|0).

Number of bytes n=32 if NB=0, else n=NB.

Stack bytes into words in CEIL(n/4)

consecutive registers starting with RT, to

R

FINAL

← ((RT + CEIL(n/4) – 1) % 32).

GPR(0) is consecutive to GPR(31).

RA is not altered unless RA = R

FINAL

.

335

Table A-1. PPC440x5 Instruction Syntax Summary (continued)

Mnemonic Operands Function

Other Registers

Changed

Page