User’s Manual

PPC440x5 CPU Core Preliminary

Page 136 of 589

mmu.fm.

September 12, 2002

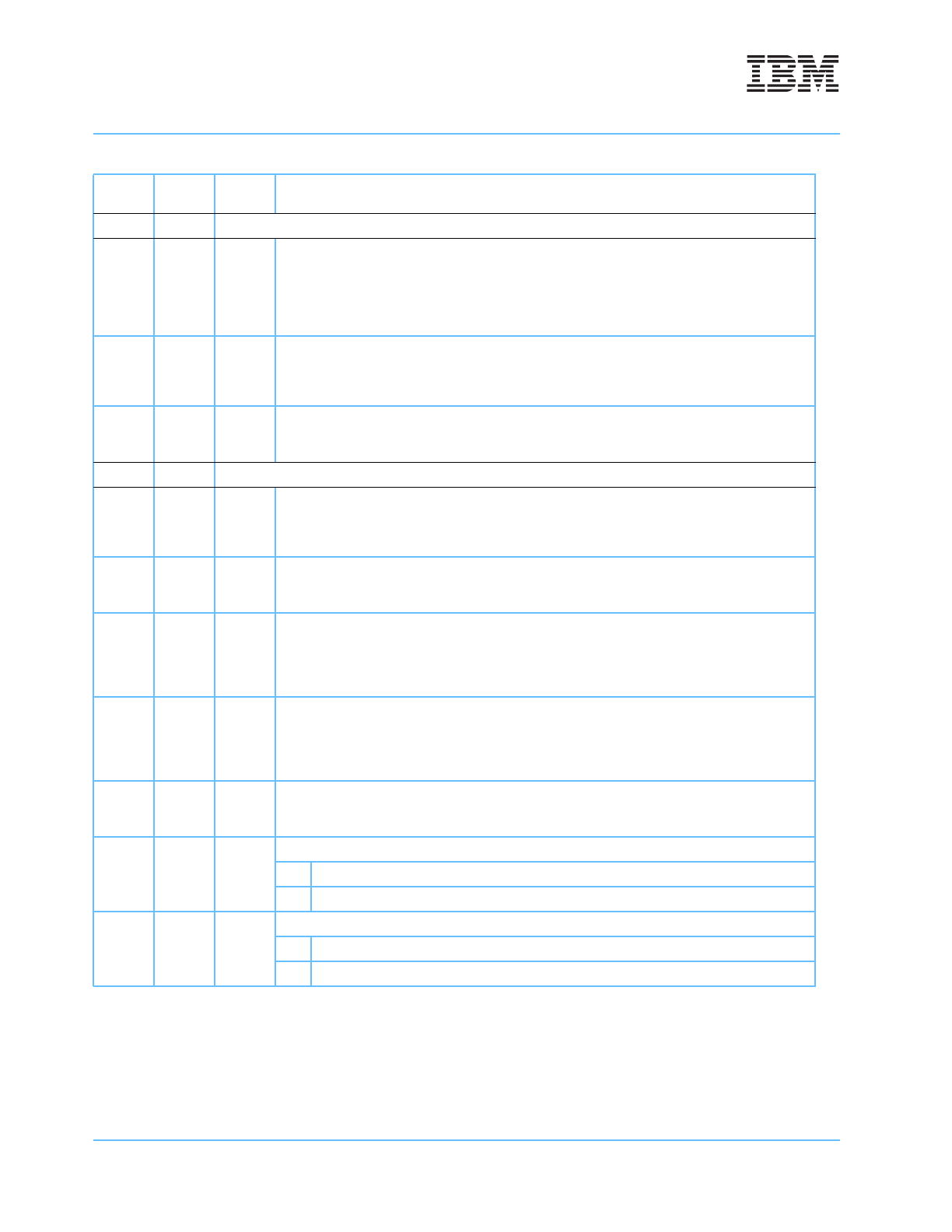

Address Translation Fields

1 0:21 RPN

Real Page Number (variable size, from 4 - 22 bits)

Bits 0:n–1 of the RPN field are used to replace bits 0:n–1 of the effective address to produce a

portion of the real address for the storage access (where n = 32–log

2

(page size in bytes) and

page size is specified by the SIZE field of the TLB entry). Software must set unused low-order

RPN bits (that is, bits n:21) to 0. See Address Translation on page 140 and Table 5-3 on

page 142.

1 22:23 PAR1

Parity for TLB word 1 (2 bits)

The PAR1 field reads the parity bits associated with TLB word 1. These bits will be loaded into a

GPR as a result of a tlbre, but are ignored when executing a tlbwe, since the parity to be writ-

ten is calculated by the processor hardware.

1 28:31 ERPN

Extended Real Page Number (4 bits)

The 4-bit ERPN field are prepended to the rest of the translated address to form a total of a 36-bit

(64 GB) real address. See Address Translation on page 140 and Table 5-3 on page 142.

Storage Attribute Fields

2 0:1 PAR2

Parity for TLB word 2 (2 bits)

The PAR2 field reads the parity bits associated with TLB word 2. These bits will be loaded into a

GPR as a result of a tlbre, but are ignored when executing a tlbwe, since the parity to be writ-

ten is calculated by the processor hardware..

216U0

User-Definable Storage Attribute 0 (1 bit) See User-Definable (U0–U3) on page 147.

Specifies the U0 storage attribute for the page associated with the TLB entry. The function of this

storage attribute is system-dependent, and has no effect within the PPC440x5 core.

217U1

User-Definable Storage Attribute 1 (1 bit) See User-Definable (U0–U3) on page 147.

Specifies the U1 storage attribute for the page associated with the TLB entry. The function of this

storage attribute is system-dependent, but the PPC440x5 core can be programmed to use this

attribute to designate a memory page as containing transient data and/or instructions (see

Instruction and Data Caches on page 95).

218U2

User-Definable Storage Attribute 2 (1 bit) See User-Definable (U0–U3) on page 147.

Specifies the U2 storage attribute for the page associated with the TLB entry. The function of this

storage attribute is system-dependent, but the PPC440x5 core can be programmed to use this

attribute to specify whether or not stores that miss in the data cache should allocate the line in the

data cache (see Instruction and Data Caches on page 95).

219U3

User-Definable Storage Attribute 3 (1 bit) See User-Definable (U0–U3) on page 147.

Specifies the U3 storage attribute for the page associated with the TLB entry. The function of this

storage attribute is system-dependent, and has no effect within the PPC440x5 core.

220W

Write-Through (1 bit) See Write-Through (W) on page 145.

0 The page is not write-through (that is, the page is copy-back).

1 The page is write-through.

221I

Caching Inhibited (1 bit) See Caching Inhibited (I) on page 145.

0 The page is not caching inhibited (that is, the page is cacheable).

1 The page is caching inhibited.

Table 5-1. TLB Entry Fields (continued)

TLB

Word

Bit Field Description