User’s Manual

Preliminary PPC440x5 CPU Core

instalfa.fm.

September 12, 2002

Page 545 of 589

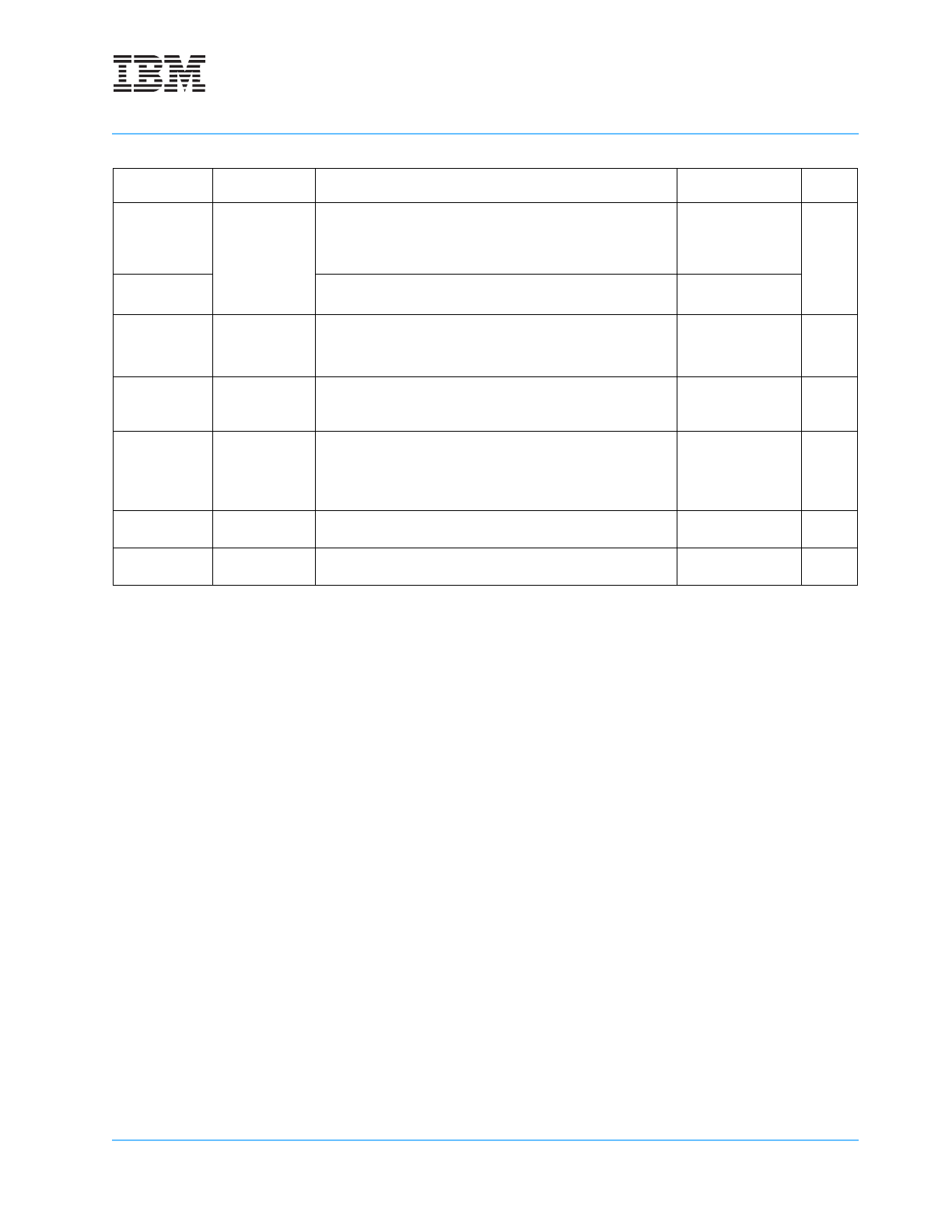

mr

RT, RS

Move register.

(RT) ← (RS)

Extended mnemonic for

or RT,RS,RS

392

mr.

Extended mnemonic for

or. RT,RS,RS

CR[CR0]

msync

Synchronization. All instructions that precede msync complete

before any instructions that follow msync begin.

When msync completes, all storage accesses initiated prior to

msync will have completed.

366

mtcr

RS

Move to Condition Register.

Extended mnemonic for

mtcrf 0xFF,RS

367

mtcrf

FXM, RS

Move some or all of the contents of RS into CR as specified by

FXM field,

mask ←

4

(FXM

0

) ||

4

(FXM

1

) || ... ||

4

(FXM

6

) ||

4

(FXM

7

).

(CR)←((RS) ∧ mask) ∨ (CR) ∧¬mask).

367

mtdcr

DCRN, RS

Move to DCR from RS,

(DCR(DCRN)) ← (RS).

368

mtmsr

RS

Move to MSR from RS,

(MSR) ← (RS).

369

Table A-1. PPC440x5 Instruction Syntax Summary (continued)

Mnemonic Operands Function

Other Registers

Changed

Page