User’s Manual

Preliminary PPC440x5 CPU Core

mmu.fm.

September 12, 2002

Page 145 of 589

5.6 Storage Attributes

Each TLB entry specifies a number of storage attributes for the memory page with which it is associated.

Storage attributes affect the manner in which storage accesses to a given page are performed. The storage

attributes (and their corresponding TLB entry fields) are:

• Write-through (W)

• Caching inhibited (I)

• Memory coherence required (M)

• Guarded (G)

• Endianness (E)

• User-definable (U0, U1, U2, U3)

All combinations of these attributes are supported except combinations which simultaneously specify a region

as write-through and caching inhibited.

5.6.1 Write-Through (W)

If a memory page is marked as write-through (W=1), then the data for all store operations to that page are

written to memory, as opposed to only being written into the data cache. If the referenced line also exists in

the data cache (that is, the store operation is a “hit”), then the data will also be written into the data cache,

although the cache line will not be marked as having been modified (that is, the “dirty” bit(s) will not be set).

See Instruction and Data Caches on page 95 for more information on the handling of accesses to write-

through storage.

5.6.2 Caching Inhibited (I)

If a memory page is marked as caching inhibited (I=1), then all load, store, and instruction fetch operations

perform their access in memory, as opposed to in the respective cache. If I=0, then the page is cacheable

and the operations may be performed in the cache.

It is a programming error for the target location of a load, store, dcbz, or fetch access to caching inhibited

storage to be in the respective cache; the results of such an access are undefined. It is not a programming

error for the target locations of the other cache management instructions to be in the cache when the caching

inhibited storage attribute is set. The behavior of these instructions is defined for both I=0 and I=1 storage.

See the instruction descriptions in Section 9 Instruction Set on page 249 for more information.

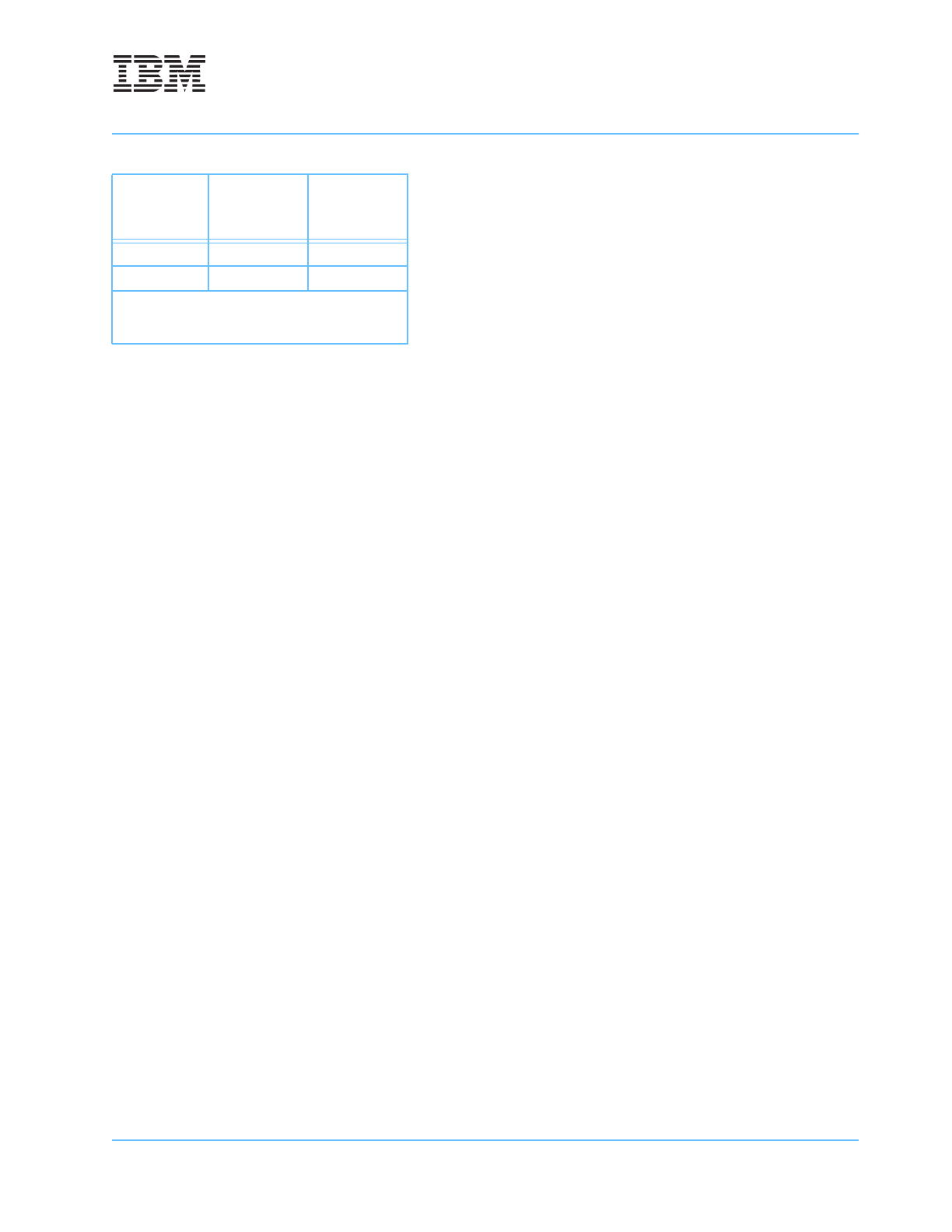

icbt

Yes

1

No

iccci

No No

1. dcbt, dcbtst, or icbt may cause a Read

Access Control exception but will not result in a Data

Storage interrupt

Table 5-4. Access Control Applied to Cache Management Instructions

Instruction

Read

Protection

Violation

Exception?

Write

Protection

Violation

Exception?