User’s Manual

PPC440x5 CPU Core Preliminary

Page 214 of 589

timers.fm.

September 12, 2002

avoid another Watchdog Timer interrupt due to the same exception (unless TCR[WIE] is cleared instead).

Watchdog Timer Interrupt on page 192 provides more information on the handling of Watchdog Timer inter-

rupts.

If TSR[WIS] is already 1 at the time of the next Watchdog Timer exception, then the action to take depends

on the value of the Watchdog Reset Control (TRC) field of the TCR. If TCR[WRC] is non-zero, then the value

of the TCR[WRC] field will be copied into TSR[WRS], TCR[WRC] will be cleared, and a core reset will occur

(see PPC440x5 Core State After Reset on page 85 for more information on core behavior when reset).

Note that once software has set TCR[WRC] to a non-zero value, it cannot be reset by software; this feature

prevents errant software from disabling the Watchdog Timer reset capability.

Table 7-3 summarizes the action to be taken upon a Watchdog Timer exception according to the values of

TSR[ENW] and TSR[WIS].

A typical system usage of the Watchdog Timer function is to enable the Watchdog Timer interrupt and the

Watchdog Timer reset function in the TCR (and MSR), and to start out with both TSR[ENW] and TSR[WIS]

clear. Then, a recurring software loop of reliable duration (or perhaps the interrupt handler for a periodic inter-

rupt such as the Fixed Interval Timer interrup) performs a periodic check of system integrity. Upon successful

completion of the system check, software clears TSR[ENW], thereby ensuring that a minimum of one full

Watchdog Timer period and a maximum of two full Watchdog Timer periods must expire before an enabled

Watchdog Timer exception will occur.

If for some reason the recurring software loop is not successfully completed (and TSR[ENW] thus not

cleared) during this period of time, then an enabled Watchdog Timer exeption will occur. This will set

TSR[WIS] and a Watchdog Timer interrupt will occur (if enabled by both TCR[WIE] and MSR[CE]). The

occurrence of a Watchdog Timer interrupt in this kind of system is interpreted as a “system error”, insofar as

the system was for some reason unable to complete the periodic system integrity check in time to avoid the

enabled Watchdog Timer exception. The action taken by the Watchdog Timer interrupt handler is of course

system-dependent, but typically the software will attempt to determine the nature of the problem and correct it

if possible. If and when the system attempts to resume operation, the software would typically clear both

TSR[WIS] and TSR[ENW], thus providing a minimum of another full Watchdog Timer period for a new system

integrity check to occur.

Finally, if for some reason the Watchdog Timer interrupt is disabled, and/or the Watchdog Timer interrupt

handler is unsuccessful in clearing TSR[WIS] and TSR[ENW] prior to another Watchdog Timer exception,

then the next exception will cause a processor reset operation to occur, according to the value of TCR[WRC].

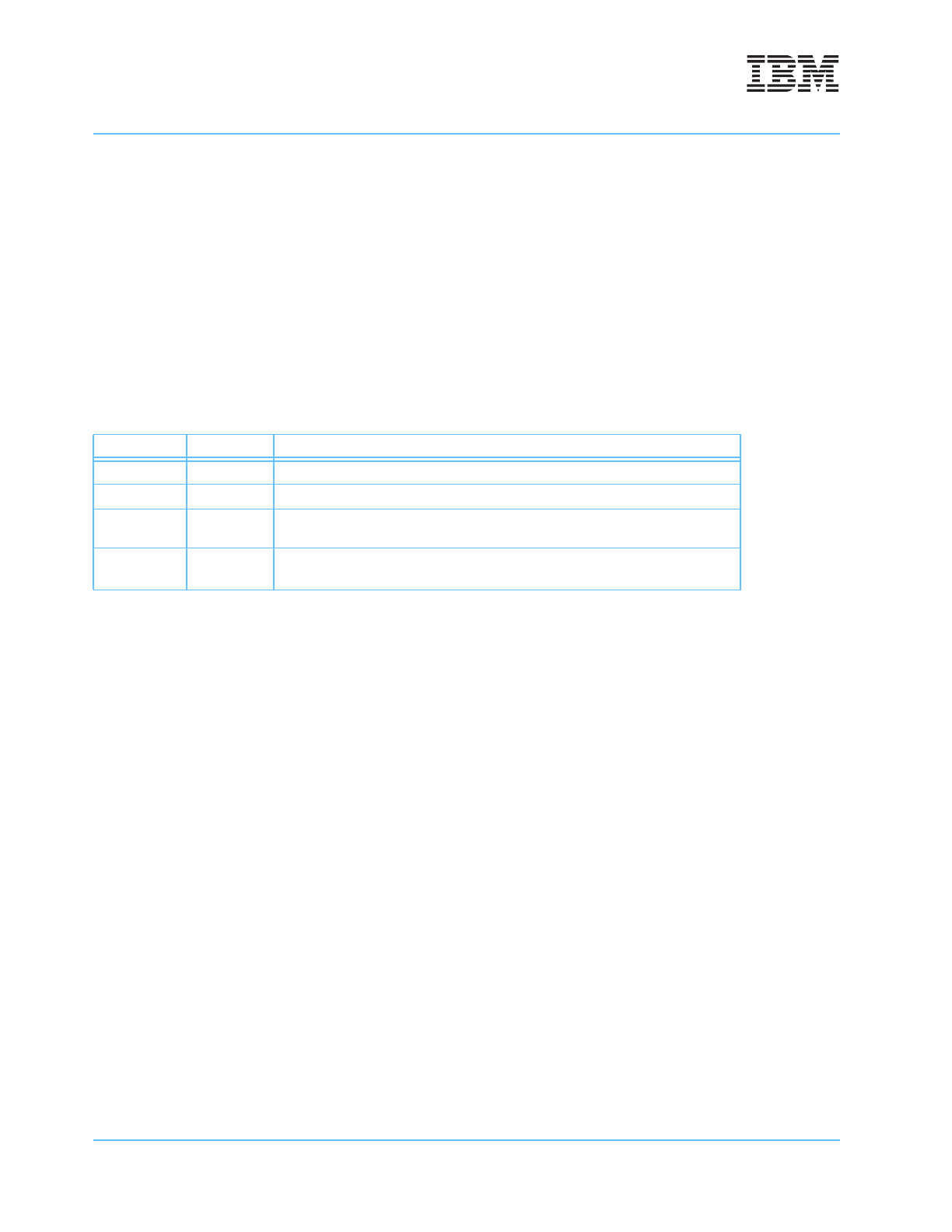

Table 7-3. Watchdog Timer Exception Behavior

TSR[ENW] TSR[WIS] Action upon Watchdog Timer exception

0 0 Set TSR[ENW] to 1

0 1 Set TSR[ENW] to 1

10

Set TSR[WIS] to 1. If Watchdog Timer interrupts are enabled (TCR[WIE]=1 and

MSR[CE]=1), then interrupt.

11

Cause Watchdog Timer reset action specified by TCR[WRC].

Reset will copy pre-reset TCR[WRC] into TSR[WRS], then clear TCR[WRC].