User’s Manual

PPC440x5 CPU Core Preliminary

Page 170 of 589

intrupts.fm.

September 12, 2002

Programming Note: An MSR bit that is reserved may be altered by rfmci, consistent with

the value being restored from MCSRR1.

MCSRR1 can be written from a GPR using mtspr, and can be read into a GPR using mfspr.

6.4.8 Data Exception Address Register (DEAR)

The DEAR contains the address that was referenced by a load, store, or cache management instruction that

caused an Alignment, Data TLB Miss, or Data Storage exception.

The DEAR can be written from a GPR using

mtspr, and can be read into a GPR using mfspr.

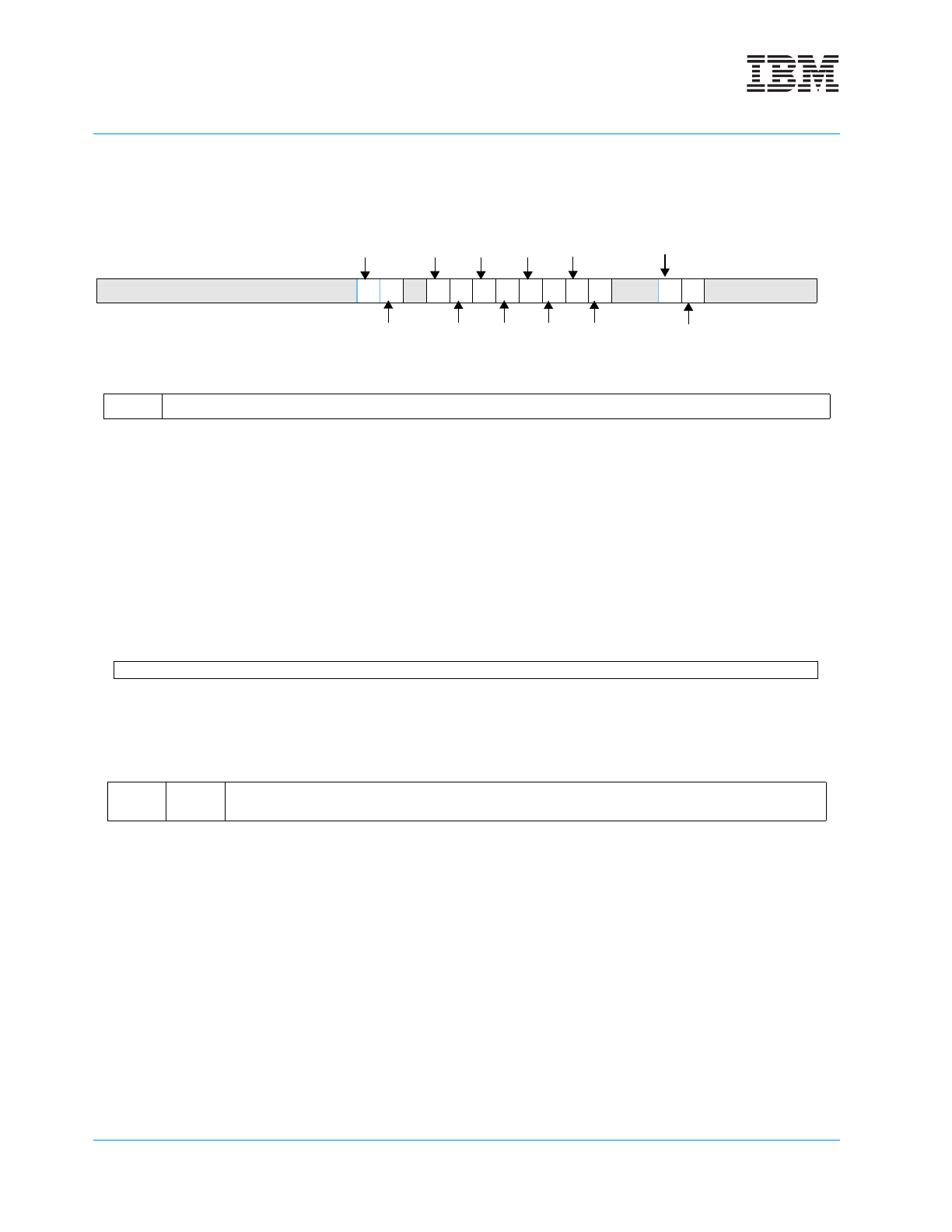

6.4.9 Interrupt Vector Offset Registers (IVOR0–IVOR15)

An IVOR specifies the quadword (16 byte)-aligned interrupt vector offset from the base address provided by

the IVPR (see Interrupt Vector Prefix Register (IVPR) on page 171) for its respective interrupt type. IVOR0–

IVOR15 are provided for the defined interrupt types. The interrupt vector effective address is formed as

follows:

IVPR

0:15

|| IVORn

16:27

|| 0b0000

where n specifies the IVOR register to be used for the particular interrupt type.

Any IVOR can be written from a GPR using mtspr, and can be read into a GPR using mfspr.

Figure 0-1. Machine Check Save/Restore Register 1 (MCSRR1)

0:31 Copy of the MSR at the time of a machine check interrupt.

Figure 6-7. Data Exception Address Register (DEAR)

0:31

Address of data exception for Data Storage, Align-

ment, and Data TLB Error interrupts

0 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 31

FE1

WE

PR

DS

CE

EE

DE

FP

ME

DWE

FE0

IS

0 31