User’s Manual

Preliminary PPC440x5 CPU Core

instalfa.fm.

September 12, 2002

Page 557 of 589

A.3 Allocated Instruction Opcodes

Allocated instructions are provided for purposes that are outside the scope of PowerPC Book-E architecture,

and are for implementation-dependent and application-specific use, including use within auxiliary processors.

Table A-2 lists the blocks of opcodes which have been allocated by PowerPC Book-E for these purposes. In

the table, the character “u” designates a secondary opcode bit which can be set to any value. In some cases,

the decimal value of a secondary opcode is shown in parentheses after the binary value.

All of the allocated opcodes listed in the table above are available for use by auxiliary processors attached to

the PPC440x5, except for those which have already been implemented within the PPC440x5 core for certain

implementation-specific purposes. As indicated in the table above, this is the case for certain secondary

opcodes within primary opcodes 4 and 31. These opcodes are identified in Table A-5 on page 559, along with

all of the defined, preserved, and reserved-nop class opcodes which are implemented within the PPC440x5

core.

A.4 Preserved Instruction Opcodes

The preserved instruction class is provided to support backward compatibility with the PowerPC Architecture,

and/or earlier versions of the PowerPC Book-E architecture. This instruction class includes opcodes which

were defined for these previous architectures, but which are no longer defined for PowerPC Book-E.

xori

RA, RS, IM

XOR (RS) with (

16

0 || IM).

Place result in RA.

449

xoris

RA, RS, IM

XOR (RS) with (IM ||

16

0).

Place result in RA.

450

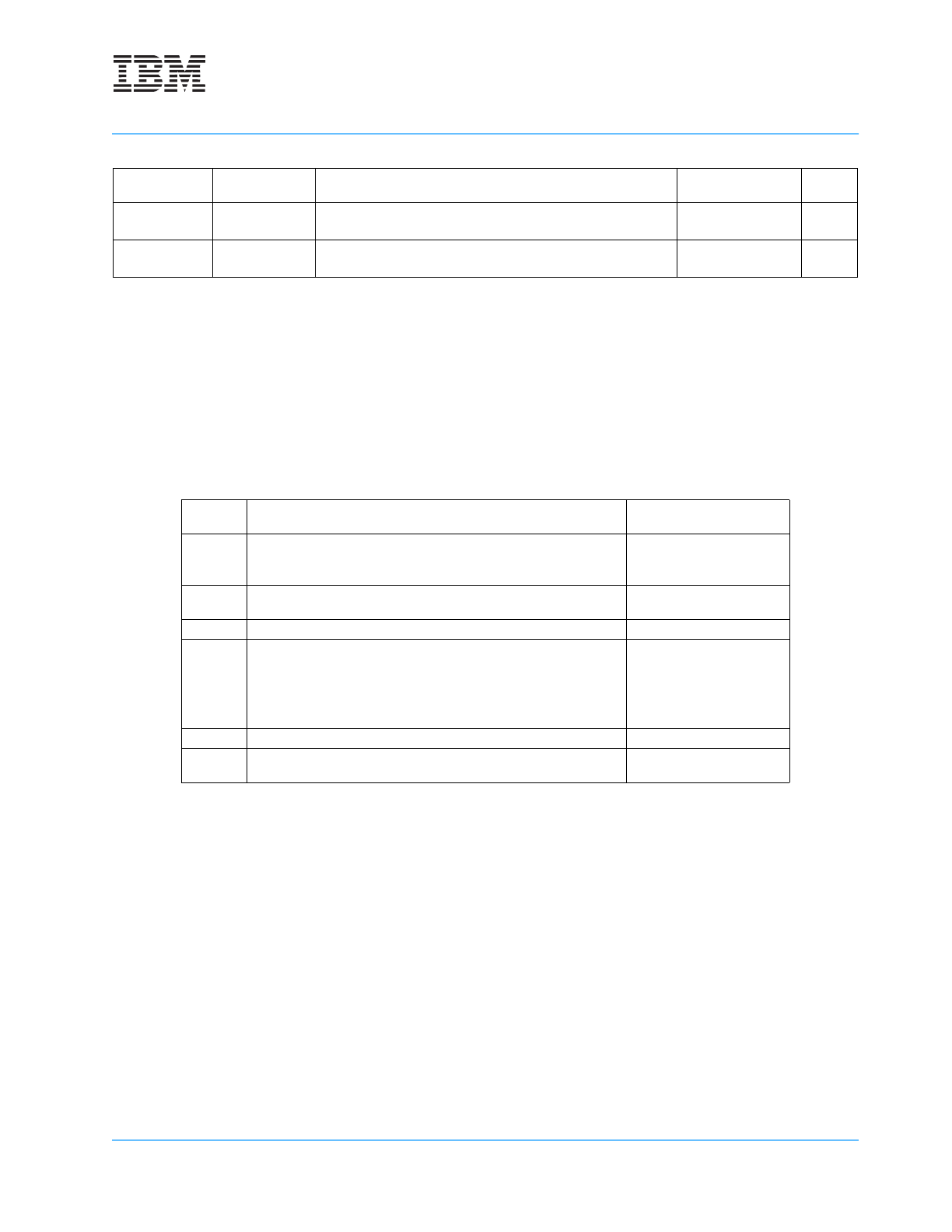

Table A-2. Allocated Opcodes

Primary

Opcode

Extended

Opcodes

PPC440x5

Usage

0

All instruction encodings (bits 6:31) except 0x00000000

(the instruction encoding of 0x00000000 is and always will be

reserved-illegal)

None

4 All instruction encodings (bits 6:31)

Various (see Table A-5 on

page 559)

19 Secondary opcodes (bits 21:30) = 0buuuuu0u11u None

31

Secondary opcodes (bits 21:30) = 0buuuuu0011u

Secondary opcodes (bits 21:30) = 0buuuuu0u110

Secondary opcode (bits 21:30) = 0b0101010110 (342)

Secondary opcode (bits 21:30) = 0b0101110110 (374)

Secondary opcode (bits 21:30) = 0b1100110110 (822)

Various (see Table A-5 on

page 559)

59 Secondary opcodes (bits 21:30) = 0buuuuu0u10u None

63

Secondary opcodes (bits 21:30) = 0buuuuu0u10u (except second-

ary opcode decimal 12, which is the fsrp defined instruction)

None

Table A-1. PPC440x5 Instruction Syntax Summary (continued)

Mnemonic Operands Function

Other Registers

Changed

Page