User’s Manual

Preliminary PPC440x5 CPU Core

prgmodel.fm.

September 12, 2002

Page 57 of 589

Table 2-4 summarizes the PPC440x5 instruction set by category. Instructions within each category are

described in subsequent sections.

2.4.1 Integer Instructions

Integer instructions transfer data between memory and the GPRs, and perform various operations on the

GPRs. This category of instructions is further divided into seven sub-categories, described below.

2.4.1.1 Integer Storage Access Instructions

Integer storage access instructions load and store data between memory and the GPRs. These instructions

operate on bytes, halfwords, and words. Integer storage access instructions also support loading and storing

multiple registers, character strings, and byte-reversed data, and loading data with sign-extension.

Table 2-5 shows the integer storage access instructions in the PPC440x5. In the table, the syntax “[u]” indi-

cates that the instruction has both an “update” form (in which the RA addressing register is updated with the

calculated address) and a “non-update” form. Similarly, the syntax “[x]” indicates that the instruction has both

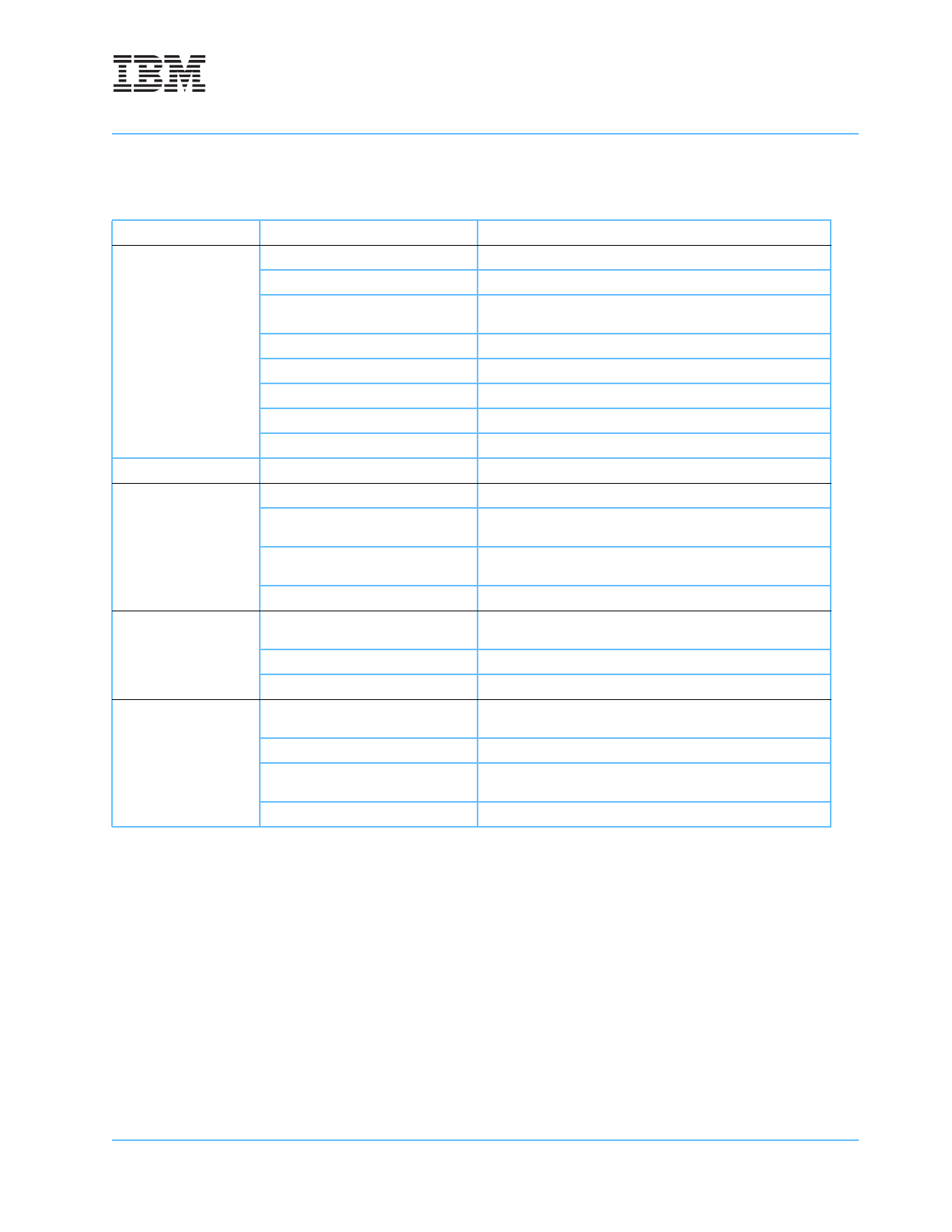

Table 2-4. Instruction Categories

Category Subcategory Instruction Types

Integer

Integer Storage Access load, store

Integer Arithmetic add, subtract, multiply, divide, negate

Integer Logical

and, andc, or, orc, xor, nand, nor, xnor, extend sign, count

leading zeros

Integer Compare compare, compare logical

Integer Select select operand

Integer Trap trap

Integer Rotate rotate and insert, rotate and mask

Integer Shift shift left, shift right, shift right algebraic

Branch

branch, branch conditional, branch to link, branch to count

Processor Control

Condition Register Logical crand, crandc, cror, crorc, crnand, crnor, crxor, crxnor

Register Management

move to/from SPR, move to/from DCR, move to/from MSR,

write to external interrupt enable bit, move to/from CR

System Linkage

system call, return from interrupt, return from critical interrupt,

return from machine check interrupt

Processor Synchronization instruction synchronize

Storage Control

Cache Management

data allocate, data invalidate, data touch, data zero, data flush,

data store, instruction invalidate, instruction touch

TLB Management read, write, search, synchronize

Storage Synchronization memory synchronize, memory barrier

Allocated

Allocated Arithmetic

multiply-accumulate, negative multiply-accumulate, multiply

halfword

Allocated Logical detect left-most zero byte

Allocated Cache Management

data congruence-class invalidate, instruction congruence-class

invalidate

Allocated Cache Debug data read, instruction read