TSR

Timer Status Register

PPC440x5 CPU Core User’s Manual Preliminary

Page 516 of 589

regsumm440core.fm.

September 12, 2002

TSR

SPR 0x150 Supervisor Read/Clear

See Timer Status Register (TSR) on page 216.

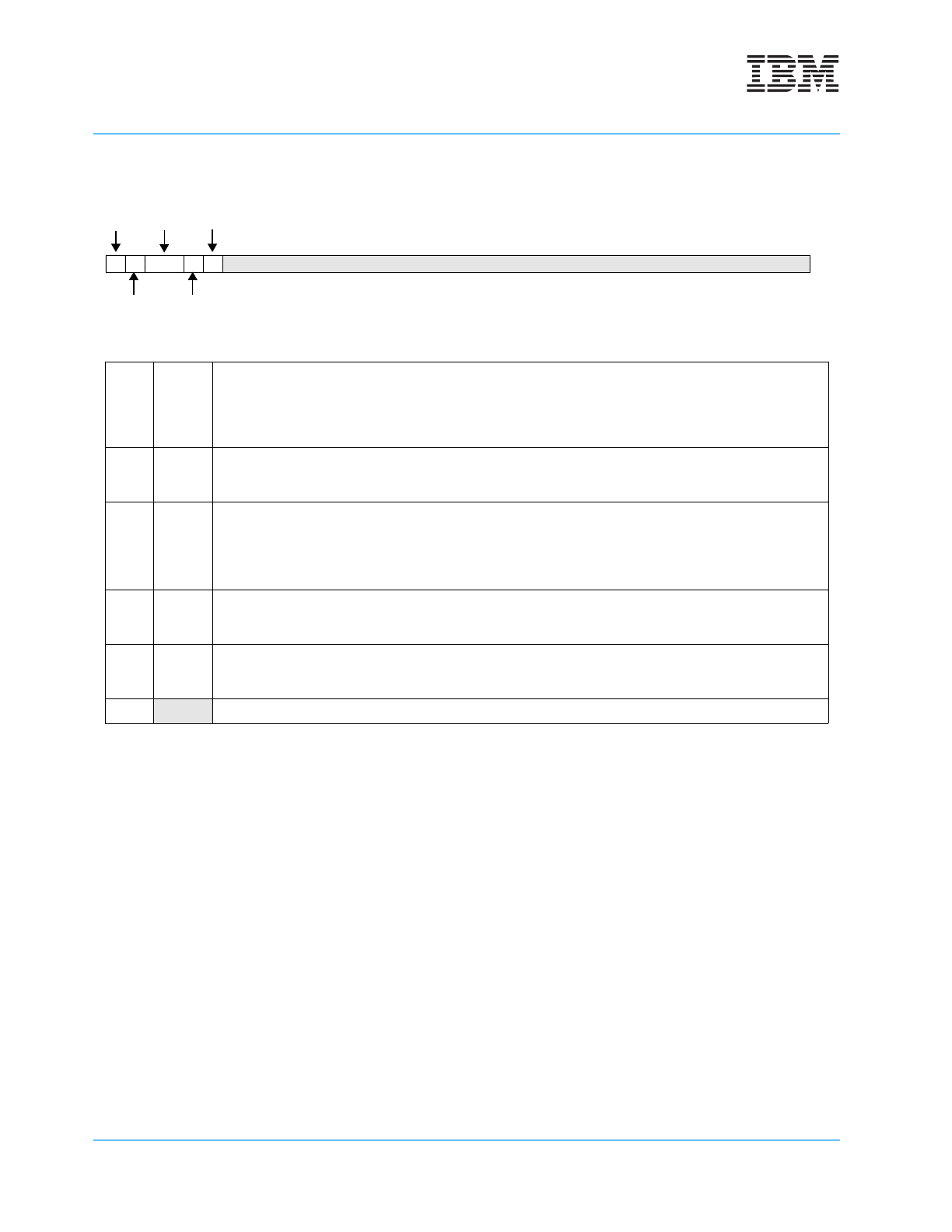

Figure 10-48. Timer Status Register (TSR)

0 ENW

Enable Next Watchdog Timer Exception

0 Action on next Watchdog Timer exception is to set

TSR[ENW] = 1.

1 Action on next Watchdog Timer exception is governed

by TSR[WIS].

1 WIS

Watchdog Timer Interrupt Status

0 Watchdog Timer exception has not occurred.

1 Watchdog Timer exception has occurred.

2:3 WRS

Watchdog Timer Reset Status

00 No Watchdog Timer reset has occurred.

01 Core reset was forced by Watchdog Timer.

10 Chip reset was forced by Watchdog Timer.

11 System reset was forced by Watchdog Timer.

4 DIS

Decrementer Interrupt Status

0 Decrementer exception has not occurred.

1 Decrementer exception has occurred.

5 FIS

Fixed Interval Timer (FIT) Interrupt Status

0 Fixed Interval Timer exception has not occurred.

1 Fixed Interval Timer exception has occurred.

6:31 Reserved

0123456 31

ENW

WIS

WRS FIS

DIS