User’s Manual

Preliminary PPC440x5 CPU Core

instalfa.fm.

September 12, 2002

Page 559 of 589

A.6 Implemented Instructions Sorted by Opcode

Table A-5 on page 559 lists all of the instructions which have been implemented within the PPC440x5 core,

sorted by primary and secondary opcode. These include defined, allocated, preserved, and reserved-nop

class instructions (see Instruction Classes on page 53 for a more detailed description of each of these

instruction classes). Opcodes which are not implemented in the PPC440x5 core are not shown in the table,

and consist of the following:

• Defined instructions

These include the floating-point operations (which may be implemented in an auxiliary processor and

executed via the AP interface), as well as the 64-bit operations and the tlbiva and mfapidi instructions,

all of which are handled as reserved-illegal instructions by the PPC440x5.

• Allocated instructions

These include all of the allocated opcodes identified in Table A-2 on page 557 which are not already

implemented within the PPC440x5 core. If not implemented within an attached auxiliary processor, these

instructions will be handled as reserved-illegal by the PPC440x5.

• Preserved instructions

These include all of the preserved opcodes identified in Table A-3 on page 558 except for the mftb

opcode (which is implemented and thus included in Table A-5). These instructions will be handled as

reserved-illegal by the PPC440x5.

• Reserved instructions

These include all of the reserved opcodes as defined by Appendix A.5 on page 558, except for the

reserved-nop opcodes identified in Table A-4 on page 558. These instructions by definition are all in the

reserved-illegal class and will be handled as such by the PPC440x5.

All PowerPC Book-E instructions are four bytes long and word aligned. All instructions have a primary opcode

field (shown as field OPCD in Figure A-1 through Figure A-9, beginning on page 522) in bits 0:5. Some

instructions also have a secondary opcode field (shown as field XO in Figure A-1 through Figure A-9).

The “Form” indicated in the table refers to the arrangement of valid field combinations within the four-byte

instruction. See Appendix A.1 on page 519, for the field layouts of each form.

Form X has a 10-bit secondary opcode field, while form XO uses only the low-order 9-bits of that field.

Form XO uses the high-order secondary opcode bit (the tenth bit) as a variable; therefore, every form XO

instruction really consumes two secondary opcodes from the 10-bit secondary-opcode space. The implicitly

consumed secondary opcode is listed in parentheses for form XO instructions in the table below.

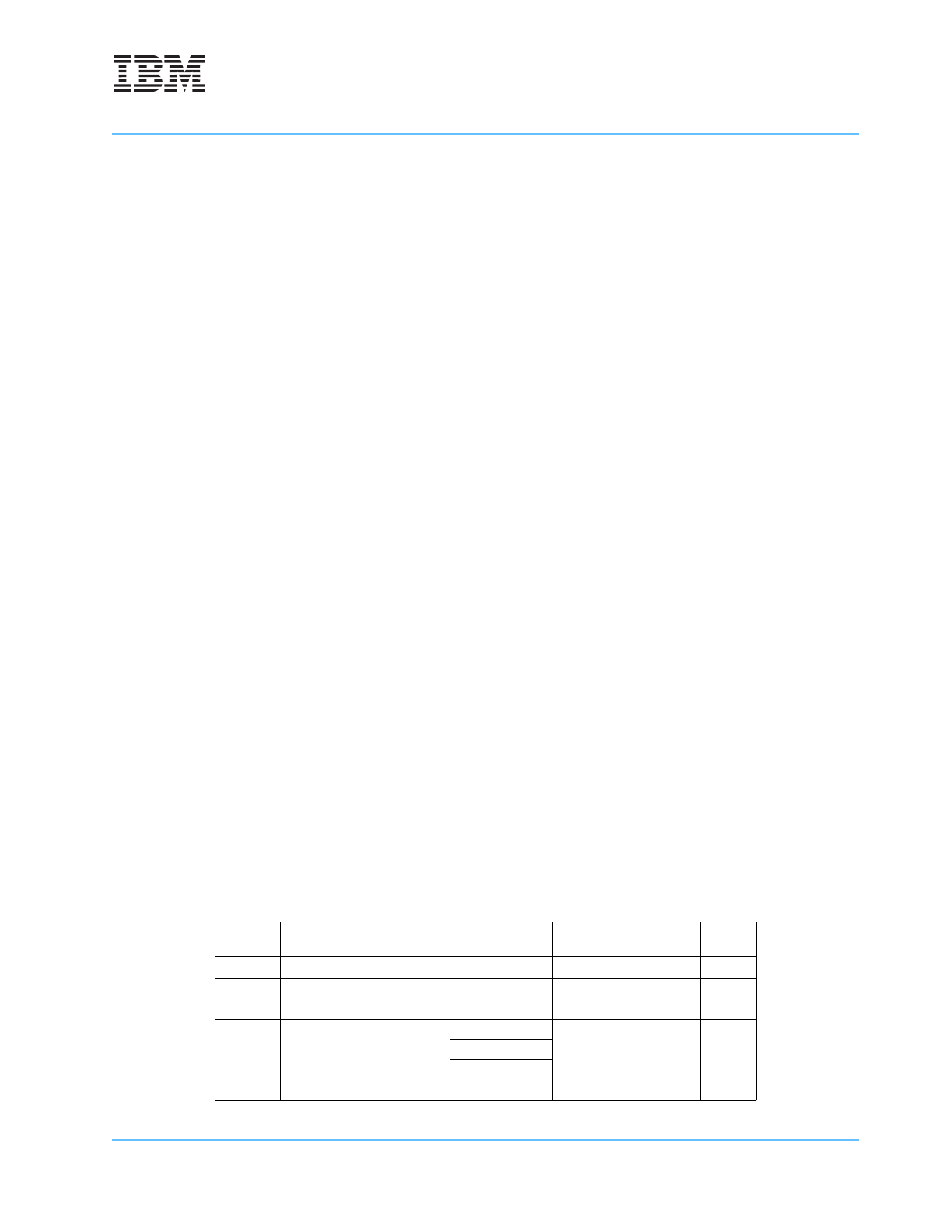

Table A-5. PPC440x5 Instructions by Opcode

Primary

Opcode

Secondary

Opcode

Form Mnemonic Operands Page

3D

twi

TO, RA, IM 443

48 X

mulhhwu

RT, RA, RB 376

mulhhwu.

4 12 (524) XO

machhwu

RT, RA, RB 352

machhwu.

machhwuo

machhwuo.