MCSR

Machine Check Status Register

PPC440x5 CPU Core User’s Manual Preliminary

Page 500 of 589

regsumm440core.fm.

September 12, 2002

MCSR

SPR 0x23C Supervisor Read/Clear

See Machine Check Status Register (MCSR) on page 174.

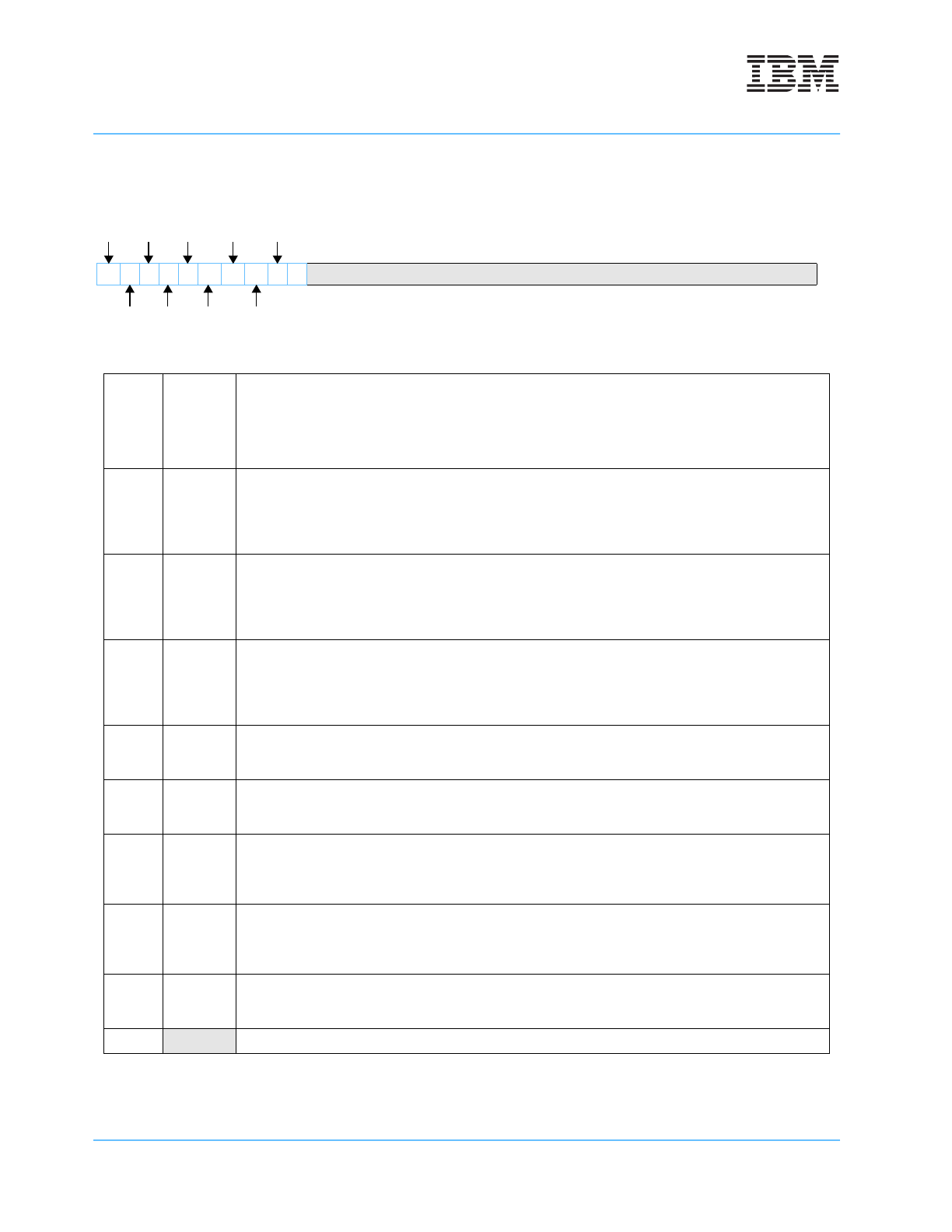

Figure 10-34. Machine Check Status Register (MCSR)

0 MCS

Machine Check Summary

0 No async machine check exception pending

1 Async machine check exception pending

Set when a machine check exception occurs

that is handled in the asynchronous fashion.

One of MCSR bits 1:7 will be set simulta-

neously to indicate the exception type. When

MSR[ME] and this bit are both set, Machine

Check interrupt is taken.

1IB

Instruction PLB Error

0 Exception not caused by Instruction Read PLB

interrupt request (IRQ)

1 Exception caused by Instruction Read PLB interrupt

request (IRQ)

2 DRB

Data Read PLB Error

0 Exception not caused by Data Read PLB interrupt

request (IRQ)

1 Exception caused by Data Read PLB interrupt

request (IRQ)

3 DWB

Data Write PLB Error

0 Exception not caused by Data Write PLB interrupt

request (IRQ)

1 Exception caused by Data Write PLB interrupt

request (IRQ)

4 TLBP

Translation Lookaside Buffer Parity Error

0 Exception not caused by TLB parity error

1 Exception caused by TLB parity error

5 ICP

Instruction Cache Parity Error

0 Exception not caused by I-cache parity error

1 Exception caused by I-cache parity error

6 DCSP

Data Cache Search Parity Error

0 Exception not caused by DCU Search parity error

1 Exception caused by DCU Search parity error

Set if and only If the DCU parity error was dis-

covered during a DCU Search operation.

See Data Cache Parity Operations on

page 129.

7 DCFP

Data Cache Flush Parity Error

0 Exception not caused by DCU Flush parity error

1 Exception caused by DCU Flush parity error

Set if and only If the DCU parity error was dis-

covered during a DCU Flush operation.

See Data Cache Parity Operations on

page 129.

8 IMPE

Imprecise Machine Check Exception

0 No imprecise machine check exception occurred.

1 Imprecise machine check exception occurred.

Set if a machine check exception occurs that

sets MCSR[MCS] (or would if it were not

already set) and MSR[ME] = 0.

9:31 Reserved

0123456789 31

M

CS

DWB

IB

DRB

IMPETLBP

ICP DCFP

DCSP