User’s Manual

Preliminary PPC440x5 CPU Core

timers.fm.

September 12, 2002

Page 215 of 589

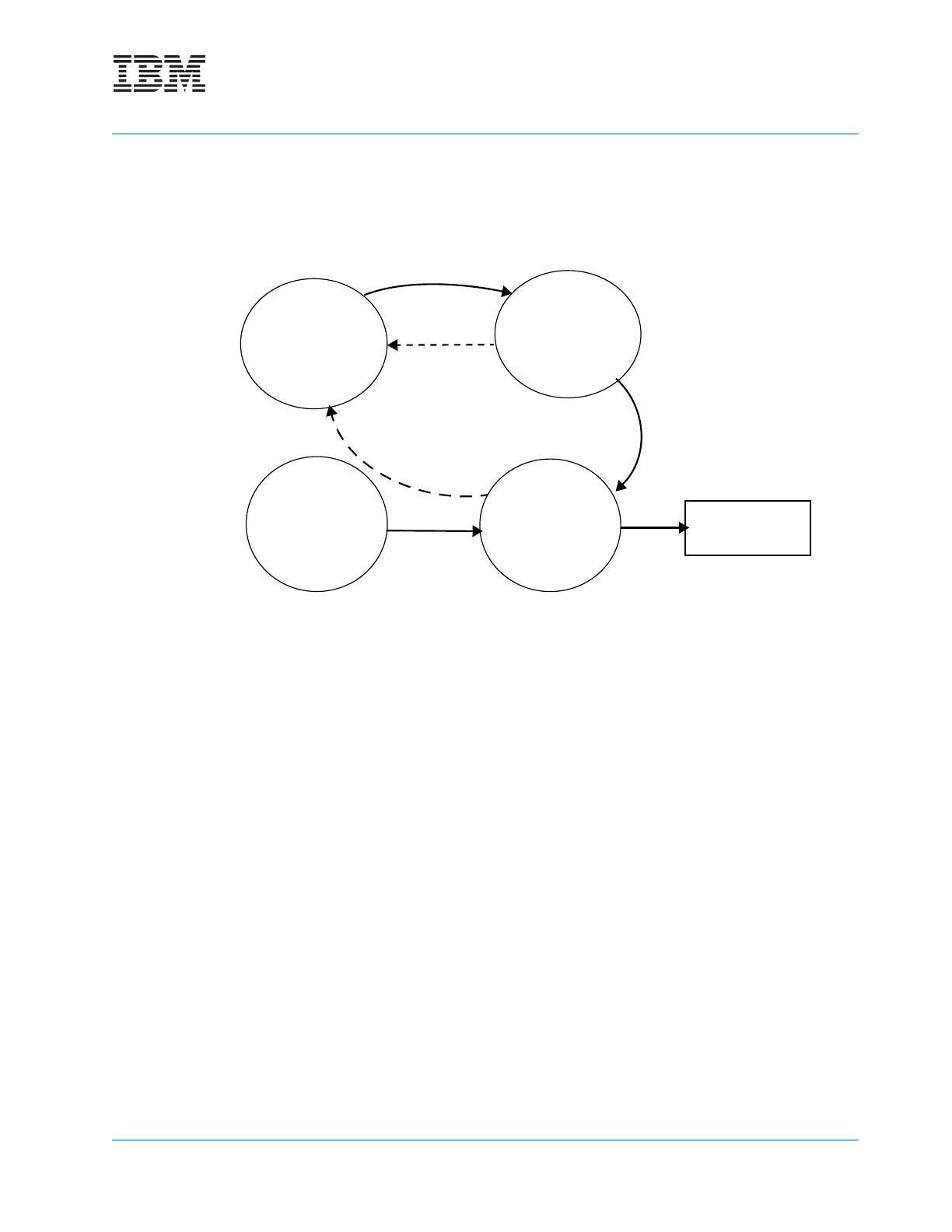

Figure 7-6 illustrates the sequence of Watchdog Timer events which occurs according to this typical system

usage.

7.5 Timer Control Register (TCR)

The TCR is a privileged SPR that controls DEC, FIT, and Watchdog Timer operation. The TCR is read into a

GPR using mfspr, and is written from a GPR using mtspr.

The Watchdog Timer Reset Control (WRC) field of the TCR is cleared to 0 by processor reset (see Chapter 3,

“Initialization”). Each bit of this 2-bit field is set only by software and is cleared only by hardware. For each bit

of the field, once software has written it to 1, that bit remains 1 until processor reset occurs. This is to prevent

errant code from disabling the Watchdog Timer reset function.

The Auto-Reload Enable (ARE) field of the TCR is also cleared to zero by processor reset. This disables

the auto-reload feature of the DEC.

TSR[ENW,WIS] = 0b00

TSR[ENW,WIS} = 0b01

TSR[ENW,WIS] = 0b10

TSR[ENW,WIS] = 0b11

Watchdog Timer exception disabled;

Watchdog Timer exception

Exception

SW Loop

subsequent exception will set TSR[WIS].

enabled; next exception sets

Figure 7-6. Watchdog State Machine

next exception sets TSR[ENW] so

TSR[WIS] and causes

interrupt if enabled by

TCR[WIE] and MSR[CE].

Exception

Exception

Exception

If TCR[WRC]

≠

0b00,

then RESET

;

else nothing.

Watchdog Timer exception disabled

but TSR[WIS] already set; this state

should not occur.

Watchdog Timer

interrupt handler

Watchdog Timer exception enabled and first

exception status still set; next exception

will cause RESET if enabled by TCR[WRC].