User’s Manual

Preliminary PPC440x5 CPU Core

prgmodel.fm.

September 12, 2002

Page 49 of 589

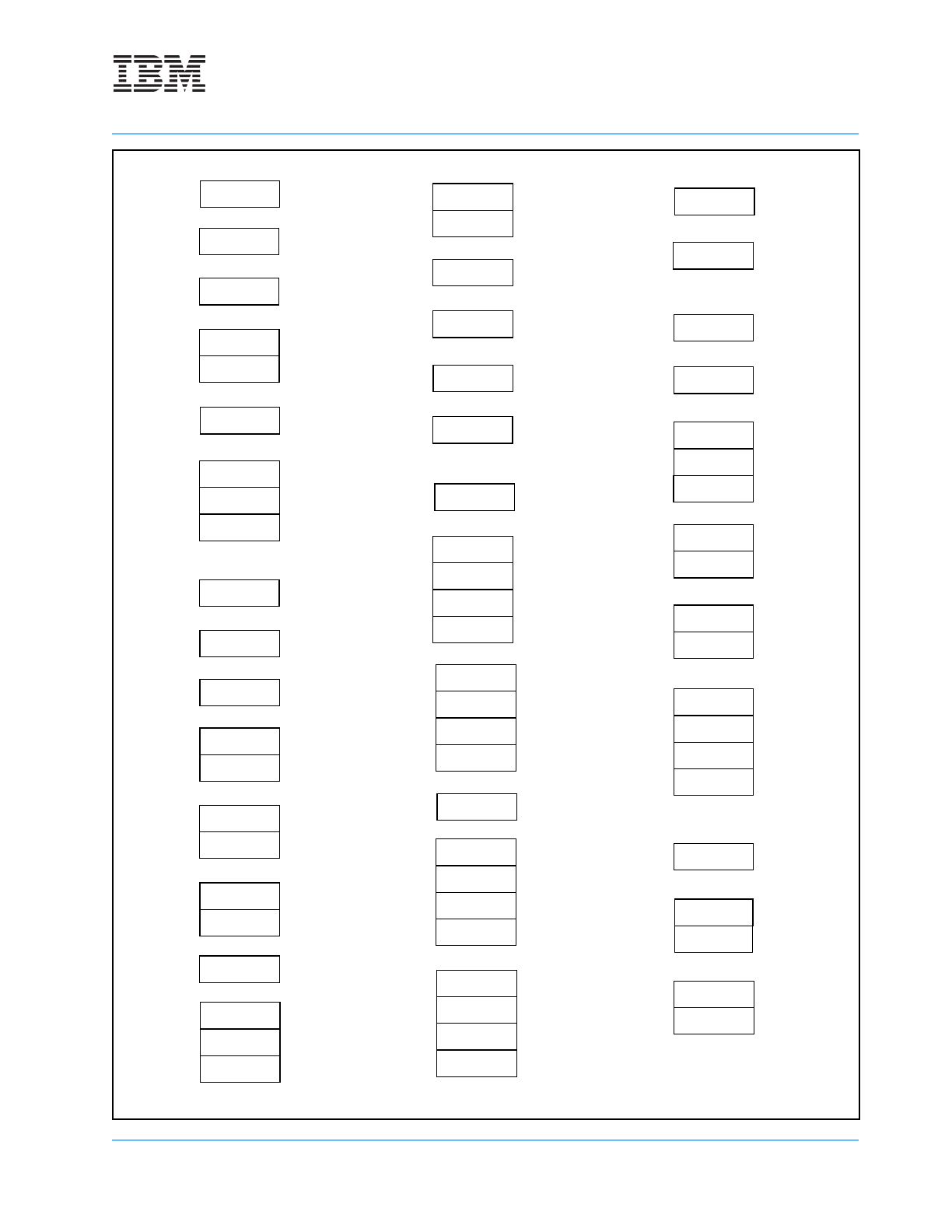

Core Configuration Registers

CCR0

CCR1

PVR

Processor Version Register

MSR

Machine State Register

Processor Control

Interrupt Processing

Interrupt Vector Prefix Register

Machine Check Syndrome Register

IVPR

MCSR

SPR General

Save/Restore Registers

SRR0

SRR1

CSRR0

CSRR1

Data Exception Address Register

DEAR

Timer Control Register

TCR

Timer Status Register

TSR

Timer

Figure 2-2. Supervisor Programming Model Registers

Instruction Address Compares

IAC1

IAC2

IAC3

IAC4

Debug

Time Base

TBU

TBL

Data Address Compares

DAC1

DAC2

Debug Status Register

DBSR

Debug Control Registers

DBCR0

DBCR1

Data Value Compares

DVC1

DVC2

Instruction Cache Debug Data Register

ICDBDR

Storage Control

Process ID

PID

MMU Control Register

MMUCR

PIR

Processor ID Register

IVOR0

IVOR15

Interrupt Vector Offset Registers

Decrementer

DEC

Decrementer Auto-Reload

DECAR

Cache Control

Instruction Cache Debug Tag Registers

ICDBTRH

ICDBTRL

Data Cache Debug Tag Registers

DCDBTRH

DCDBTRL

INV0

INV1

INV2

INV3

Instruction Cache Normal Victim

ITV0

ITV1

ITV2

ITV3

Instruction Cache Transient Victim

DNV0

DNV1

DNV2

DNV3

Data Cache Normal Victim

DTV0

DTV1

DTV2

DTV3

Data Cache Transient Victim

SPRG0

SPRG7

•

•

•

Debug Data Register

DBDR

DBCR2

Instruction Cache Victim Limit

IVLIM

Data Cache Victim Limit

DVLIM

Critical Save/Restore Registers

Cache Debug

•

•

•

Reset Configuration

RSTCFG

MCSRR0

MCSRR1

Machine Check Save/Restore Registers

Exception Syndrome Register

ESR