Preliminary PPC440x5 CPU Core User’s Manual

instrset.fm.

September 12, 2002 Page 253 of 589

9.3.1 Operator Precedence

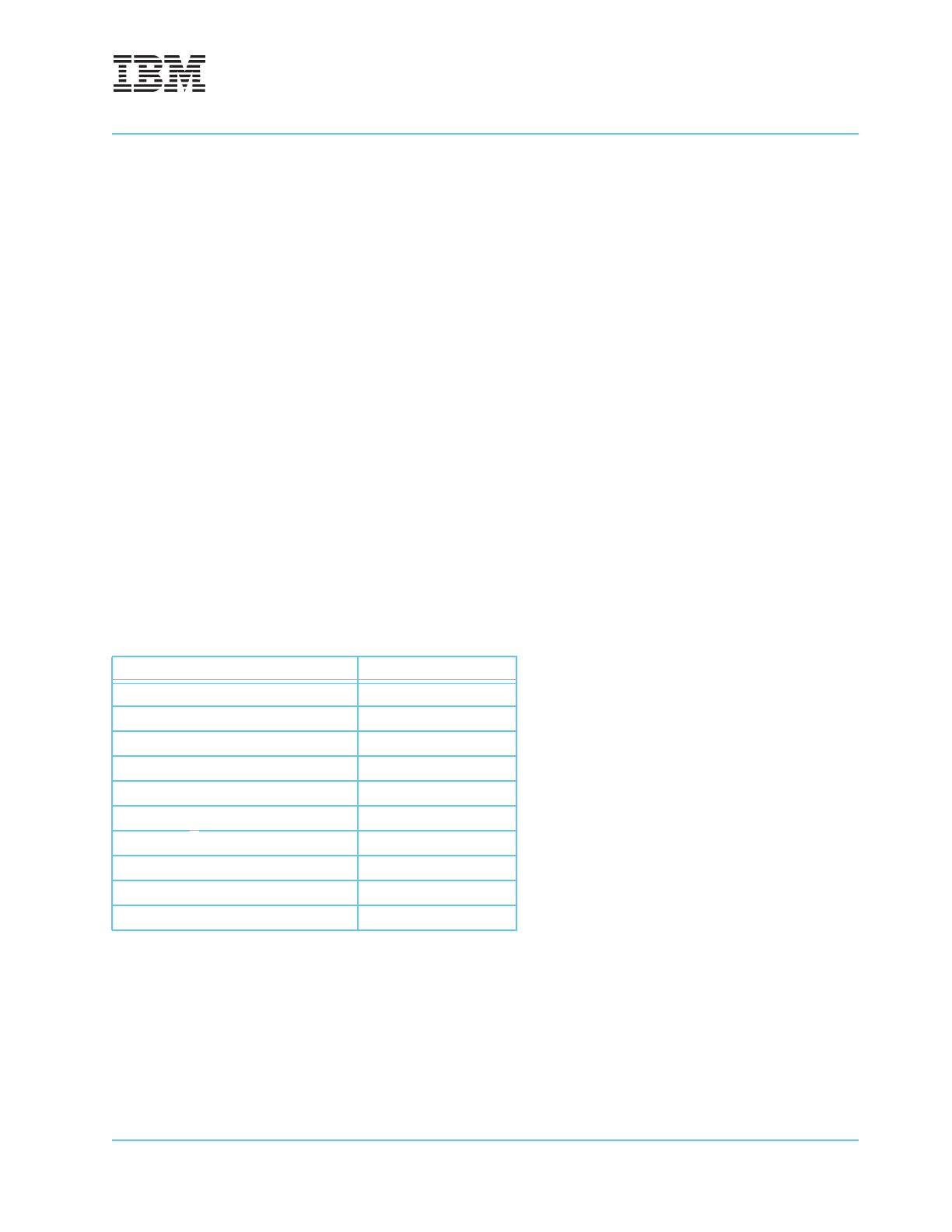

Table 9-3 lists the pseudocode operators and their associativity in descending order of precedence:

9.4 Register Usage

Each instruction description lists the registers altered by the instruction. Some register changes are explicitly

detailed in the instruction description (for example, the target register of a load instruction). Some instructions

also change other registers, but the details of the changes are not included in the instruction descriptions.

instruction(EA) An instruction operating on a data or instruction cache block associated

with an EA.

leave Leave innermost do loop or do loop specified in a leave statement.

n A decimal number

n

b The bit or bit value b is replicated n times.

xx Bit positions which are don’t-cares.

|| Concatenation

× Multiplication

÷ Division yielding a quotient

⊕ Exclusive-OR (XOR) logical operator

– Twos complement subtraction, unary minus

¬ NOT logical operator

∧ AND logical operator

∨ OR logical operator

Table 9-3. Operator Precedence

Operators Associativity

REG

b

, REG[FLD], function evaluation Left to right

n

b Right to left

¬, – (unary minus) Right to left

×, ÷ Left to right

+, – Left to right

|| Left to right

=, ≠, <, >, , Left to right

∧, ⊕ Left to right

∨ Left to right

← None

<

u

>

u