User’s Manual

PPC440x5 CPU Core Preliminary

Page 174 of 589

intrupts.fm.

September 12, 2002

6.4.12 Machine Check Status Register (MCSR)

The MCSR contains status to allow the Machine Check interrupt handler software to determine the cause of a

machine check exception. Any Machine Check exception that is handled as an asynchronous interrupt sets

MCSR[MCS] and other appropriate bits of the MCSR. If MSR[ME] and MCSR[MCS] are both set, the

machine will take a Machine Check interrupt. See Machine Check Interrupt on page 178.

The MCSR is read into a GPR using mfspr. Clearing the MCSR is performed using mtspr by placing a 1 in

the GPR source register in all bit positions which are to be cleared in the MCSR, and a 0 in all other bit posi-

tions. The data written from the GPR to the MCSR is not direct data, but a mask. A 1 clears the bit and a 0

leaves the corresponding MCSR bit unchanged.

29:31 PCRF

Program Interrupt—Condition Register Field

If ESR[PCRE]=1, this field indicates which CR field

was to be updated by the floating-point instruction

which caused the exception.

This is an implementation-dependent field of the

ESR and is not part of the PowerPC Book-E Archi-

tecture.

This field is only defined for a Floating-Point

Enabled exception type Program interrupt, and

then only when ESR[PIE] is 0.

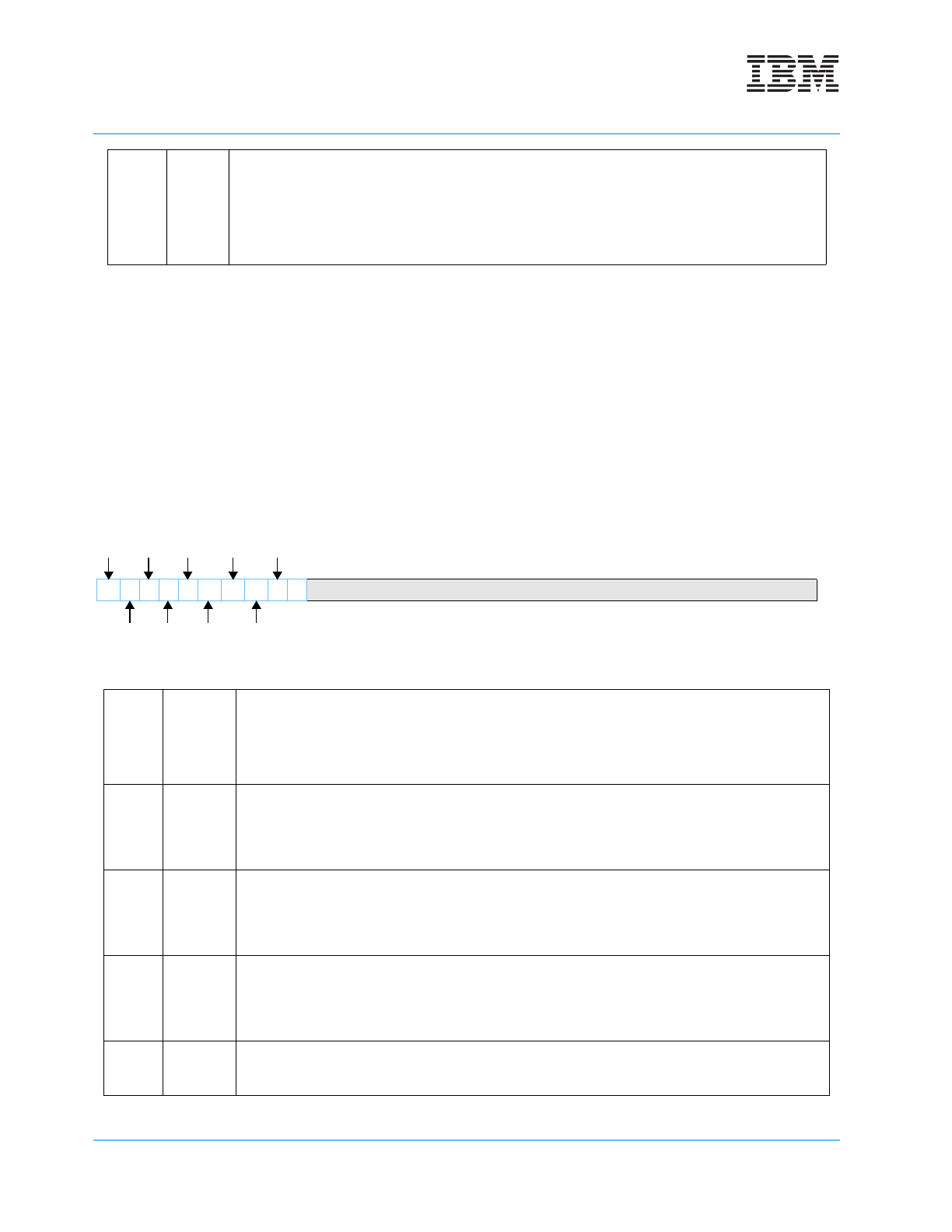

Figure 6-11. Machine Check Status Register (MCSR)

0 MCS

Machine Check Summary

0 No async machine check exception pending

1 Async machine check exception pending

Set when a machine check exception occurs

that is handled in the asynchronous fashion.

One of MCSR bits 1:7 will be set simulta-

neously to indicate the exception type. When

MSR[ME] and this bit are both set, Machine

Check interrupt is taken.

1IB

Instruction PLB Error

0 Exception not caused by Instruction Read PLB

interrupt request (IRQ)

1 Exception caused by Instruction Read PLB interrupt

request (IRQ)

2 DRB

Data Read PLB Error

0 Exception not caused by Data Read PLB interrupt

request (IRQ)

1 Exception caused by Data Read PLB interrupt

request (IRQ)

3 DWB

Data Write PLB Error

0 Exception not caused by Data Write PLB interrupt

request (IRQ)

1 Exception caused by Data Write PLB interrupt

request (IRQ)

4 TLBP

Translation Lookaside Buffer Parity Error

0 Exception not caused by TLB parity error

1 Exception caused by TLB parity error

0123456789 31

M

CS

DWB

IB

DRB

IMPETLBP

ICP DCFP

DCSP