TMP92CZ26A

92CZ26A-98

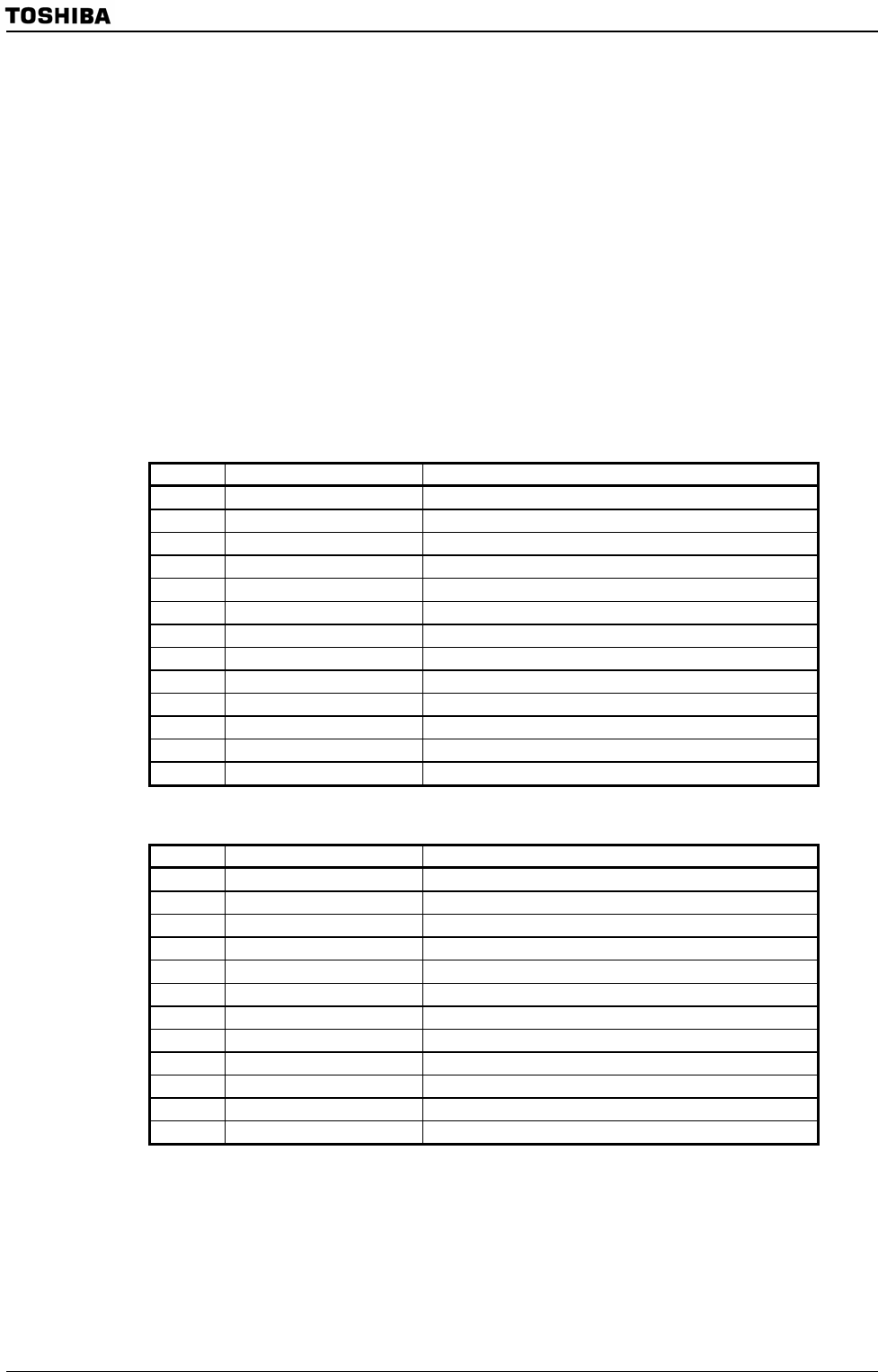

3.6.4 Setting Example

This section explains how to set the DMAC using an example.

(1) Transferring music data from internal RAM to I2S by DMA transfer

The 32 Kbytes of data stored in the internal RAM at addresses 2000H to 9FFFH shall be

transferred to FIFO-RAM via I2S. Each time an INTI2S request is asserted, 64 bytes (4

bytes x 16 times) shall be transferred to FIFO-RAM using DMAC channel 0. Since INTI2S

is an FIFO empty interrupt, the first data must be set in advance. Therefore, only the first

64 bytes shall be transferred by DMA soft start. After 32 Kbytes have been transferred, the

INTDMA0 interrupt routine shall be activated to prepare for the next processing.

(a) Main routine

No Instruction Comments

1 ldl (hdmas0),2000H ; Source address = 2000H

2 ldl (hdmad0),i2sbuf ; Destination address = i2sbuf

3 ldw (hdmaca0),16 ; Counter A = 16

4 ldw (hdmacb0),512 ; Counter B = 512 (32768/64)

5 ldb (hdmam0),0AH ; Transfer mode = source INC, 4 bytes

6 set 0,(hdmae) ; Enable DMA channel 0.

7 ld (dmar),01H ; Transfer the first 64 bytes by DMA soft start.

8 nop ;

9 ld (dma0v),i2s_vector ; INTI2S = DMA0

10 ld (intedma01),xxH ; INTDMA level = x

11 ldw (i2sctl0),xxxxH ; Set operation mode for I2S.

12 ldw (i2sctl1),xxxxH ; Start I2S transmission.

13 ei xx ; Enable CPU interrupts.

(b) INTDMA0 interrupt routine

No Instruction Comments

1 res 0,(hdmae) ; Disable DMA channel 0.

2 :

3 :

4 :

5 :

6

7

8

9

10

11 reti ;