TMP92CZ26A

92CZ26A-259

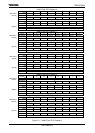

3. Read

Reading valid data

; ***** Read valid data*****

;

ldw (ndfmcr0),2010h ; CE0 enable

ldw (ndfmcr0),20B0h ; WE enable, CLE enable

ld (ndfdtr0),00h ; Read command

ldw (ndfmcr0),20D0h ; ALE enable

ld (ndfdtr0),xxh ; Address write (3 or 4 times)

;

; Wait setup time (from Busy to Ready)

; 1. Flag polling

; 2. Interrupt

;

ldw (ndfmcr0),2015h ; Reset ECC, ECCE enable, CE0 enable

ld xx,(ndfdtr0) ; Data read (512 times)

ldw (ndfmcr0),2010h ; ECC circuit disable

ld xx,(ndfdtr0) ; Redundancy data read (8 times)

ld xx,(ndfdtr0) ; ECC data read (3 times)

ld xx,(ndfdtr0) ; Redundancy data read (2 times)

ld xx,(ndfdtr0) ; ECC data read (3 times)

Generating ECC Reading ECC

; ***** Read ECC *****

;

ldw (ndfmcr0),2010h ; ECC circuit disable

ldw xxxx,(ndeccrd0) ; Read ECC from internal circuit

; 1’st Read: D15-0 > LPR15:0 For first 256 bytes

ldw xxxx,(ndeccrd1) ; Read ECC from internal circuit

; 2’nd Read: D15-0 > FFh+CPR5:0+11b For first 256 bytes

ldw xxxx,(ndeccrd0) ; Read ECC from internal circuit

; 3’rd Read: D15-0 > LPR15:0 For second 256 bytes

ldw xxxx,(ndeccrd1) ; Read ECC from internal circuit

; 4’th Read: D15-0 > FFh+CPR5:0+11b For second 256 bytes

Software processing

The ECC data generated for the read operation and the ECC in the

redundant area in the NAND Flash are compared. If any error is found, the

error processing routine is performed to correct the error data. For details,

see

3.11.3.2 “Error Correction Methods”.