TMP92CZ26A

92CZ26A-14

3. Operation

This section describes the basic components, functions and operation of the TMP92CZ26A.

3.1 CPU

The TMP92CZ26A contains an advanced high-speed 32-bit CPU (900/H1 CPU)

3.1.1 CPU Outline

900/H1 CPU is high-speed and high-performance CPU based on 900/L1 CPU. 900/H1

CPU has expanded 32-bit internal data bus to process Instructions more quickly.

Outline is as follows:

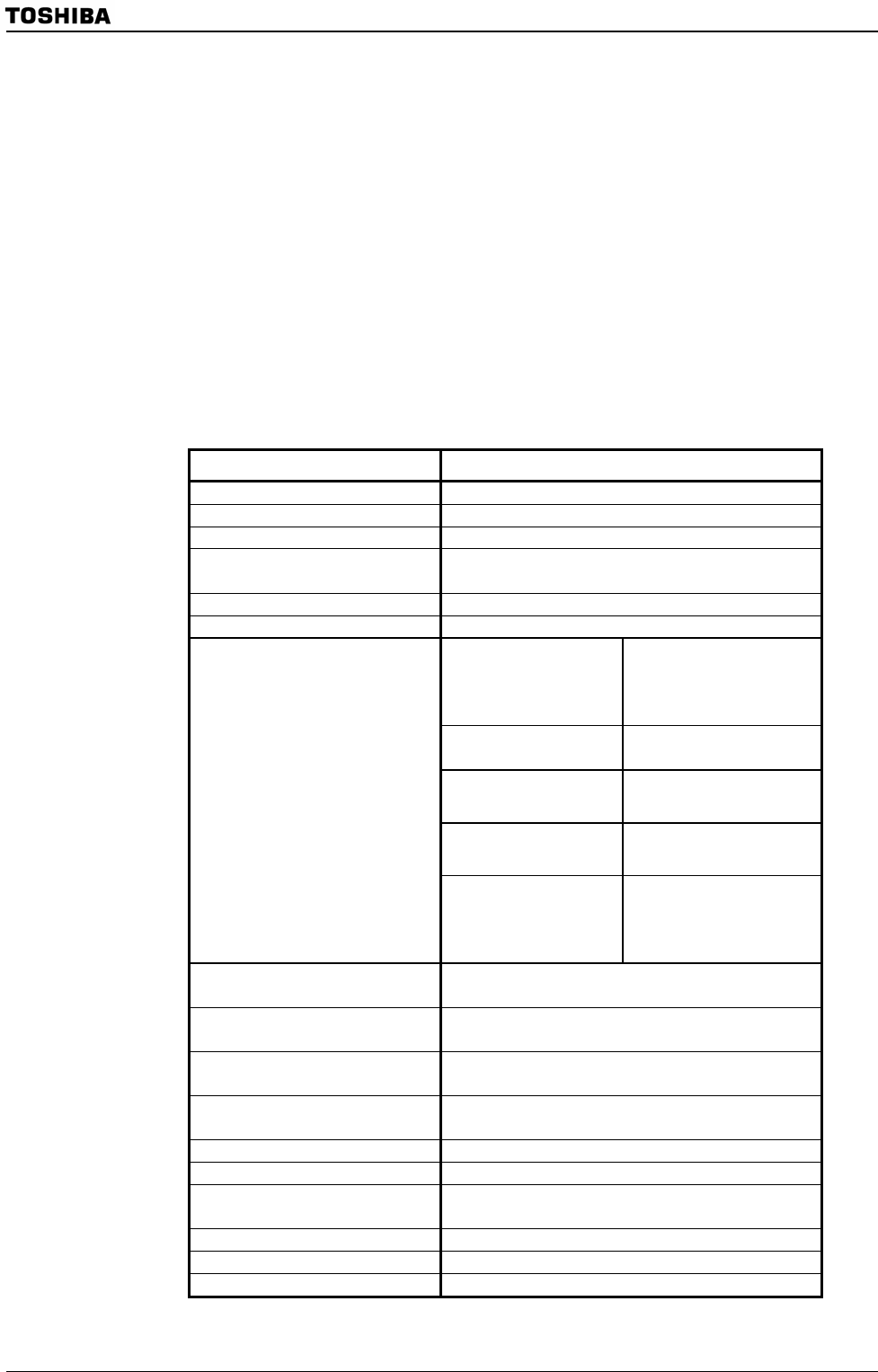

Table 3.1.1Outline of TMP92CZ26A

Parameter TMP92CZ26A

Width of CPU Address Bus 24-bit

Width of CPU Data Bus 32-bit

Internal Operating Frequency Max 80MHz

Minimum Bus Cycle 1-clock access

(12.5ns at 80MHz)

Internal RAM 32-bit 2-1-1-1 clock access

Internal Boot ROM 32 bit 2-clock access

8-bit,

2-clock access

INTC,SDRAMC,

MEMC,LCDC,

TSI,PORT,

PMC

16-bit,

2-clock access

MMU,USB,

NDFC,SPIC,DMAC

32-bit,

2-clock access

I2S

MAC

32-bit,

1-clock access

MAC

Internal I/O

8-bit,

5 to 6-clock access

TMRA,TMRB,

SIO,RTC,

MLD/ALM, SBI

CGEAR,ADC,WDT

External memory

(SRAM, MASKROM etc.)

8/16-bit 2-clock access

(can insert some waits)

External memory

(SDRAM)

16-bit 1-clock access

External memory

(NAND FLASH)

8/16-bit 2-clock access

(can inset some waits)

Minimum Instruction

Execution Cycle

1-clock(12.5ns at 80MHz)

Conditional Jump 2-clock(25.0ns at 80MHz)

Instruction Queue Buffer 12-byte

Instruction Set Compatible with TLCS-900/L1

(LDX instruction is deleted)

CPU mode Only maximum mode

Micro DMA 8-channel

Hardware DMA 6-channel