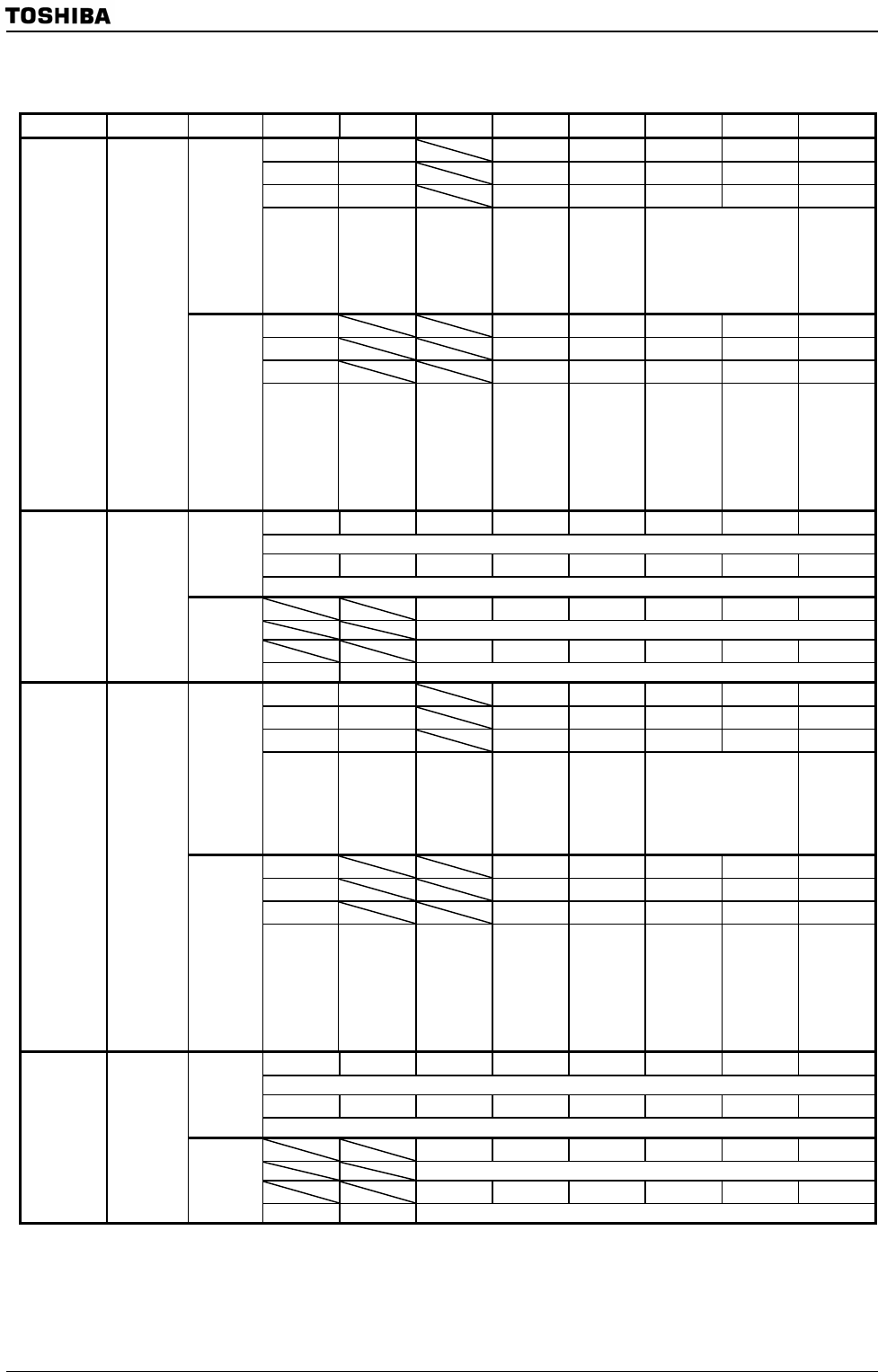

TMP92CZ26A

92CZ26A-745

(22) I

2

S (2/2)

Symbol Name

Address 7 6 5 4 3 2 1 0

TXE0 *CNTE0 DIR0 BIT0 DTFMT01 DTFMT00 SYSCKE0

R/W R/W R/W R/W R/W R/W R/W

0 0 0 0 0 0 0

1808H

Transmit

0: Stop

1: Start

Counter

control

0: Clear

1: Start

Transmis

sion start

BIT

0:MSB

1:LSB

Bit length

0: 8 bits

1:16 bits

Output format

00: I2S

10: Right

01: Left

11:Reserved

System

clock

0:Disable

1:Enable

CLKS0 FSEL0 TEMP0 WLVL0 EDGE0 CLKE0

R/W R/W R R/W R/W R/W

0 0 1 0 0 0

I2S0CTL

I2S

Control

Register0

1809H

Source

clock

0: f

SYS

1: f

PLL

Stereo

/monaural

0: Stereo

1: Monaural

Condition of

transmission

FIFO

0: data

1: None

data

WS level

0:low left

1:high left

Clock

edge for

data

output

0:Rising

1:Falling

Clock

enable

(After trans-

mission)

0:Operate

1:Stop

CK07 CK06 CK05 CK04 CK03 CK02 CK01 CK00

R/W

0 0 0 0 0 0 0 0

180AH

Divider value for CK signal (8-bit counter)

WS05 WS04 WS03 WS02 WS01 WS00

R/W

0 0 0 0 0 0

I2S0C

I2S0

Divider

Value

Setting

Register

180BH

Divider value for WS signal (6-bit counter)

TXE1 *CNTE1 DIR1 BIT1 DTFMT11 DTFMT10 SYSCKE1

R/W R/W R/W R/W R/W R/W R/W

0 0 0 0 0 0 0

1818H

Transmit

0: Stop

1: Start

Counter

control

0: Clear

1: Start

Transmis

sion start

BIT

0:MSB

1:LSB

Bit length

0: 8 bits

1:16 bits

Output format

00: I2S 10:

Right

01: Left

11:Reserved

System

clock

0:Disable

1:Enable

CLKS1 FSEL1 TEMP1 WLVL1 EDGE1 CLKE1

R/W R/W R R/W R/W R/W

0 0 1 0 0 0

I2S1CTL

I2S

Control

Register1

1819H

Source

clock

0: f

SYS

1: f

PLL

Stereo

/monaural

0: Stereo

1: Monaural

Condition of

transmission

FIFO

0: data

1: None

data

WS level

0:low left

1:high left

Clock

edge for

data

output

0:Rising

1:Falling

Clock

enable

(After trans-

mission)

0:Operate

1:Stop

CK17 CK16 CK15 CK14 CK13 CK12 CK11 CK10

R/W

0 0 0 0 0 0 0 0

181AH

Set divide frequency for CK signal (8-bit counter)

WS15 WS14 WS13 WS12 WS11 WS10

R/W

0 0 0 0 0 0

I2S1C

I2S1

Divider

Value

Setting

Register

181BH

Set divided frequency for WS signal (6-bit counter)