TMP92CZ26A

92CZ26A-639

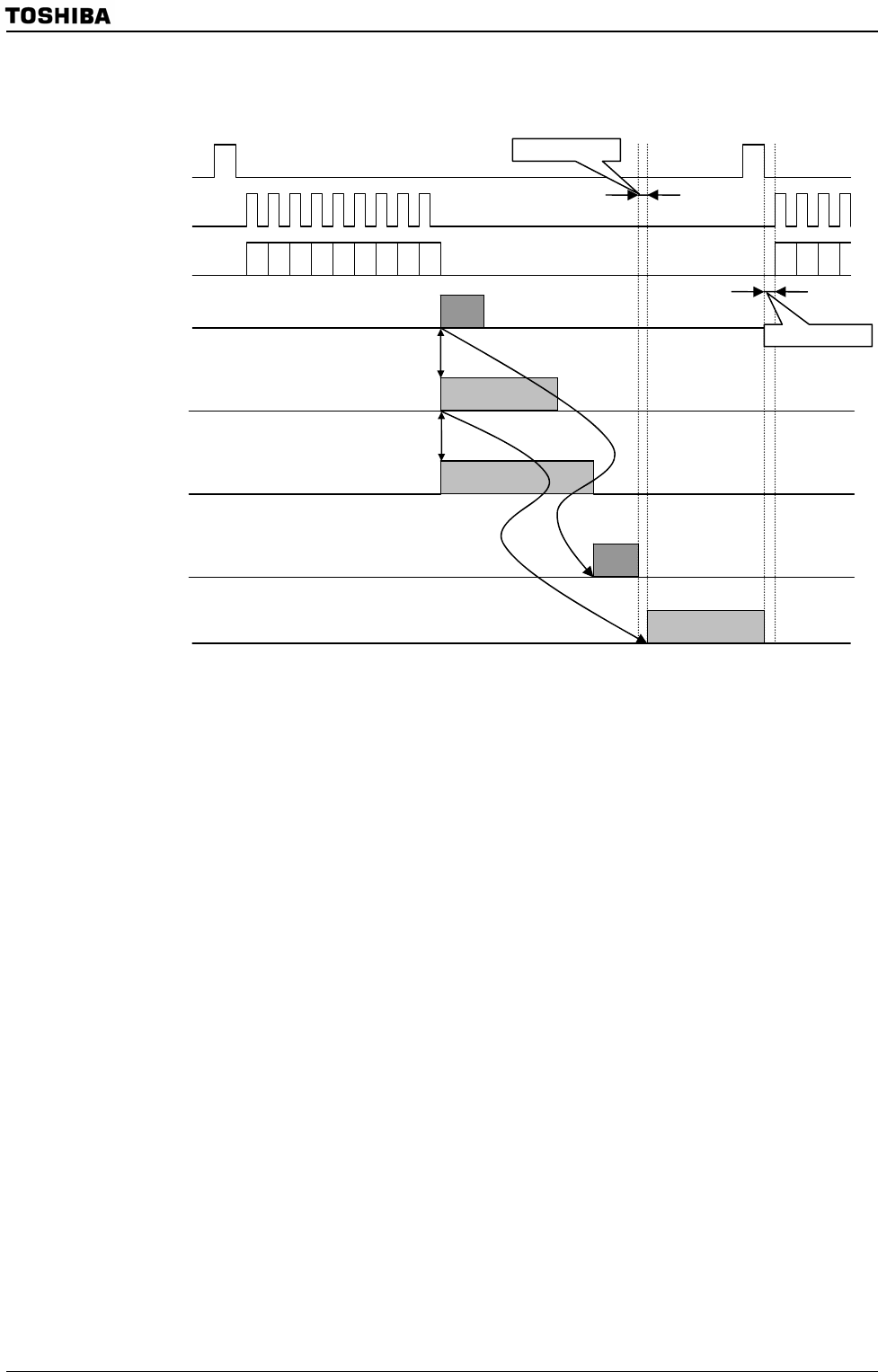

Figure 3.27.2 Example of Data Bus Occupancy Timing in Debug Mode

Figure 3.27.2 shows an example of data bus occupancy timing in debug mode. If the steal

program issues a wait request immediately before the DMA operation for the LCD (LCD

DMA operation 1) and HDMA (HDMA operation 1) are asserted, these operations must

wait until the steal program is finished before they can be performed. (LCD DMA is given a

higher priority than HDMA in bus arbitration. This means that bus requests is

sued for LCD DMA and HDMA while the steal program is running are processed in the

order of LCD and HDMA (LCD DMA operation 2 → HDMA operation 2) regardless of the

order in which they are issued. )

Taking the above into account, it is necessary to ensure that each LCD DMA or HDMA

operation is finished before the next LCD driver output is started.

In other words, to avoid abnormal operation in debug mode, the maximum duration of

HDMA operation time must be set so that it does not interfere with LCD DMA operation.

Alternatively, the LHSYNC period should be adjusted to accommodate a wait request by

the steal program (80 times of transmission for debug clock: LH_SYNCLK), although this

slightly reduces the LCD display quality.

LHSYNC

LCP0

LD-bus

LCD DMA operation 1

HDMA operation 1

(Worst case)

LCD DMA operation 2

Setup time 1

Setup time 2

HDMA operation 2

Steal operation

(Worst case)

1

2

3