TMP92CZ26A

92CZ26A-663

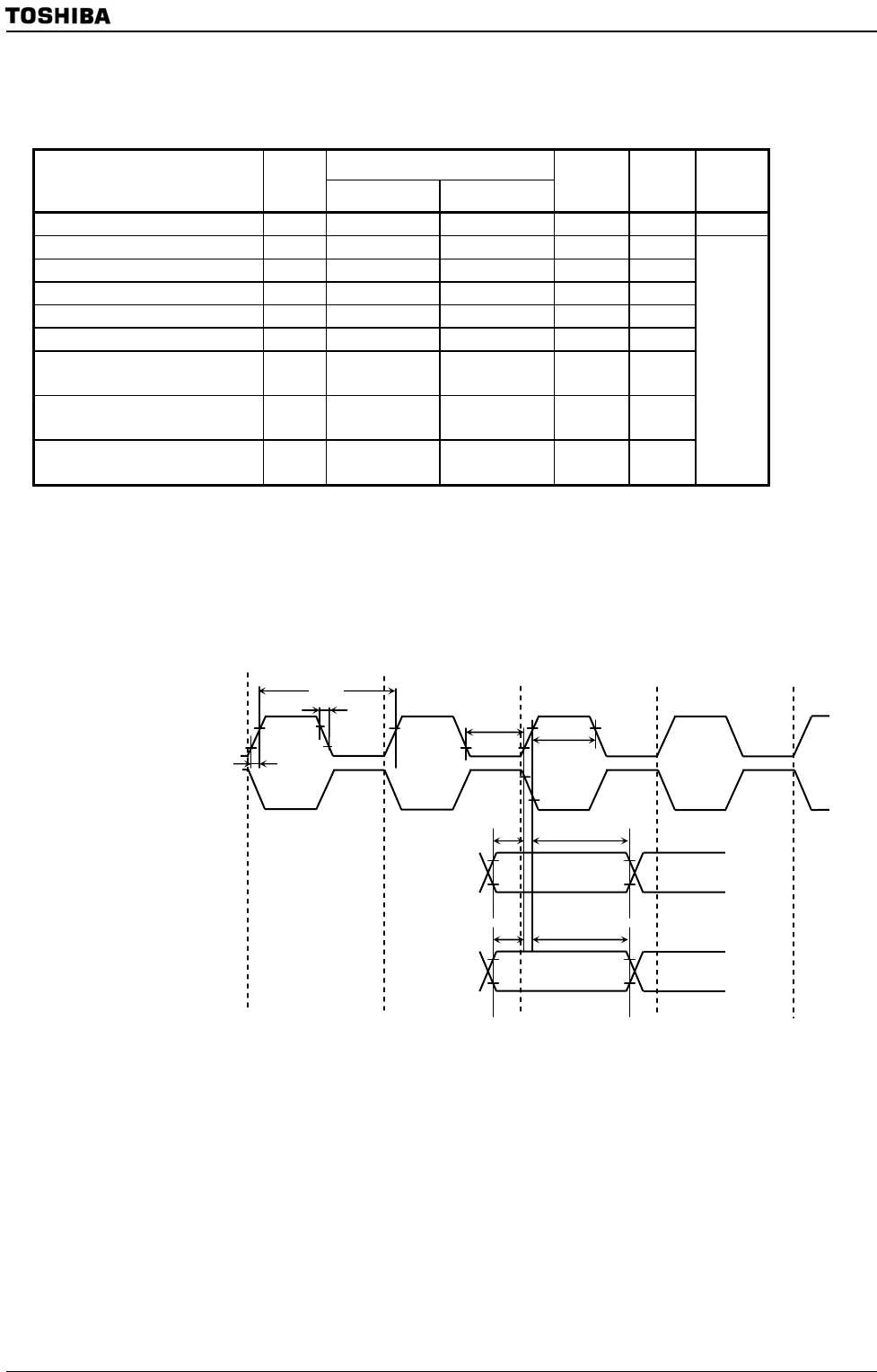

4.3.11 SPI Controller

Variable

Parameter Symbol

Min Max

80MHz 60 MHz Unit

SPCLK frequency ( = 1/S)

f

PP

20 20 15 MHz

SPCLK rising time

t

r

6 6 6

SPCLK falling time

t

f

6 6 6

SPCLK low width

t

WL

0.5S

− 6 19 28

SPCLK high width

t

WH

0.5S

− 6 19 28

Output data valid → SPCLK rising

t

ODS

0.5S

− 18 7 15

SPCLK rising/ falling

→ Output data hold

t

ODH

0.5S

− 10 15 23.4

Input data valid

→ SPCLK rising/ falling

t

IDS

5 5 5

SPCLK rising/ falling

→ Input data valid

t

IDH

5 5 5

ns

AC measuring condition

• Clock of top column in above table shows system clock frequency, and “S” in “Variable” show

SPCLK clock cycle [ns].

• C

L

= 25 pF

SPCLK Output

(at SPIMD<TCPOL,RCPOL>= “11”)

SPDO Output

f

PP

t

r

t

f

0.2V

CC

0.7 V

CC

t

WL

t

WH

t

ODS t

ODH

t

IDS

t

IDH

SPDI Input

SPCLK Output

(at SPIMD<TCPOL,RCPOL>= “00”)