TMP92CZ26A

92CZ26A-287

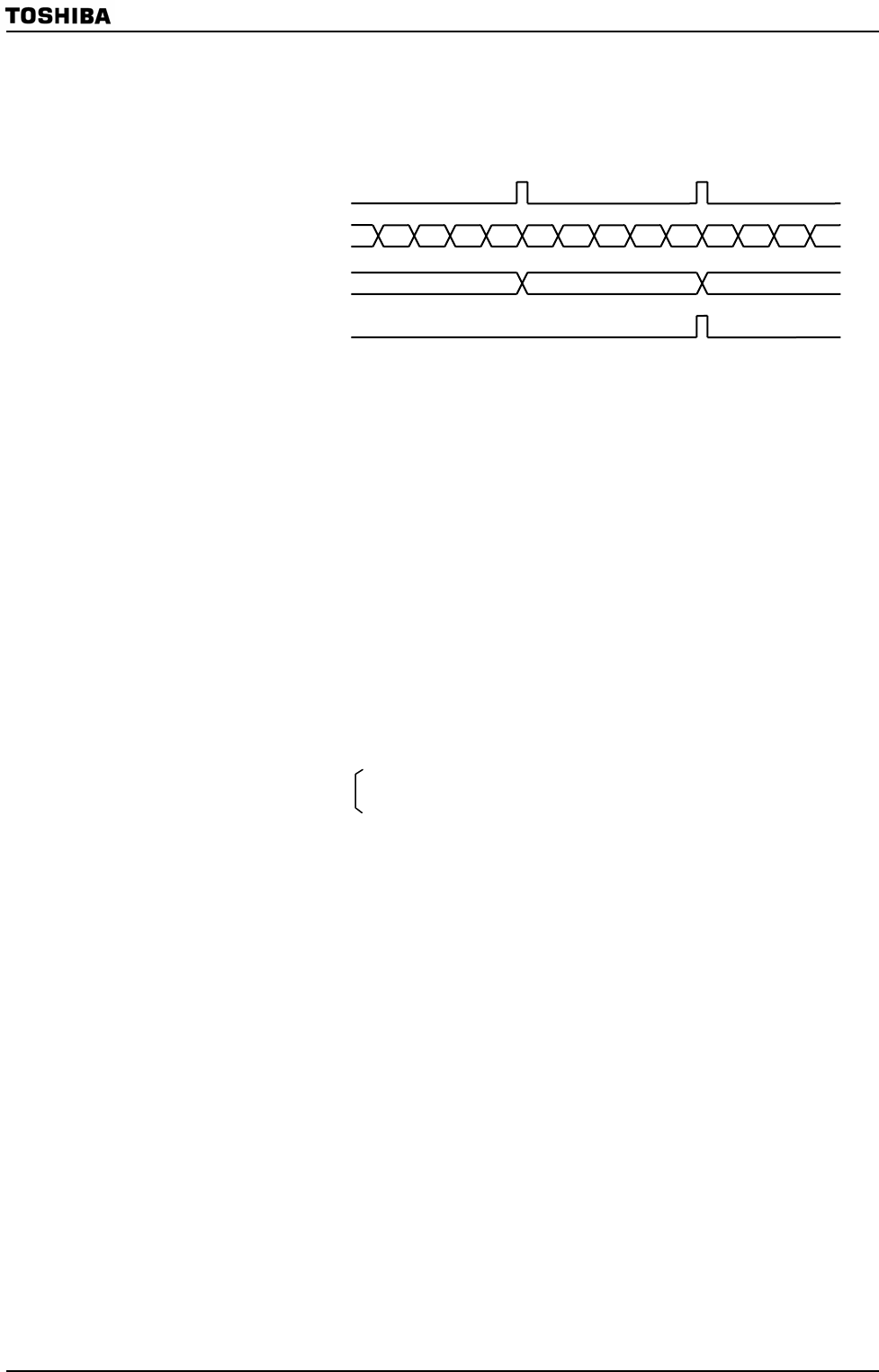

c. Making TMRA1 count up on the match signal from the TMRA0 comparator

Select 8-bit timer mode and set the comparator output from TMRA0 to be the

input clock to TMRA1.

Figure 3.12.18 TMRA1 Count Up on Signal from TMRA0

(2) 16 bit timer mode

Pairing the two 8-bit timers TMRA0 and TMRA1 configures a 16-bit interval timer.

To make a 16-bit interval timer in which TMRA0 and TMRA1 are cascaded together,

set TA01MOD<TA01M1:0> to 01.

In 16-bit timer mode, the overflow output from TMRA0 is used as the input clock for

TMRA1, regardless of the value set in TA01MOD<TA01CLK1:0>.

Table 3.12.2shows

the relationship between the timer (Interrupt) cycle and the input clock selection.

Example: To generate an INTTA1 interrupt every 0.13 s at f

SYS

= 50 MHz, set the timer registers

TA0REG and TA1REG as follows:

* Clock state Clcok gear : 1/1

Prescaler of clock gear : 1/2

If φT16 (2.6 μs at f

SYS

= 50 MHz) is used as the input clock for counting, set the following

value in the registers: 0.13 s ÷ 2.6 μs = 50000 = C350H; e.g. set TA1REG to C3H and

TA0REG to 50H.

2 3451 2345 12 31

1 2 1

Comparator output

(TMRA0 match)

TMRA0 up counter

(when TA0REG = 5)

TMRA1 up counter

(when TA1REG = 2)

TMRA1 match out

p

ut