TMP92CZ26A

92CZ26A-628

3.26 Multiply and Accumulate Calculation Unit (MAC)

The TMP92CZ26A includes a multiply-accumulate unit (MAC) capable of 32-bit × 32-bit + 64-bit

arithmetic operations at high speed. The MAC has the following features:

One-cycle execution for all MAC operations (excluding register access time)

Three operation modes : 1) 64-bit + 32-bit × 32-bit

2) 64-bit − 32-bit × 32-bit

3) 32-bit × 32-bit − 64-bit

Support for signed/unsigned operations

Support for integer operations only

3.26.1 Registers

The MAC in the TMP92CZ26A has one control register and three data registers. These

registers are connected to the CPU via a 32-bit bus and can be accessed in one system clock

(f

SYS

).

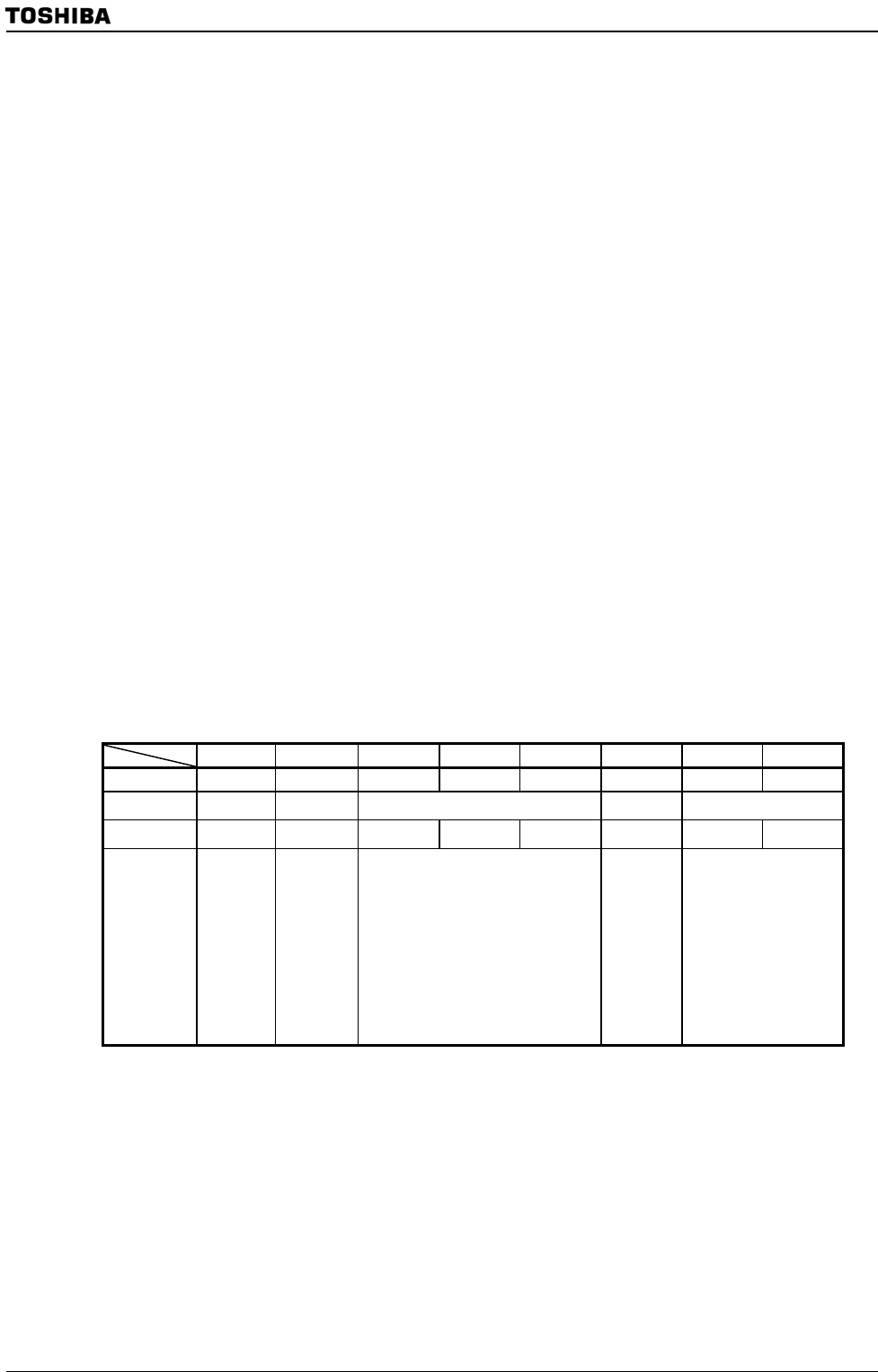

3.26.1.1 Control Register

The control register is used to control the operation of the MAC.

MAC Control Register

7 6 5 4 3 2 1 0

bit Symbol MOVF MOPST MSTTG2 MSTTG1 MSTTG0 MSGMD MOPMD1 MOPMD0

Read/Write R/W W R/W R/W R/W

After reset 0 0 0 0 0 0 0 0

Function

Overflow

flag

0: No

overflow

1: Overflow

occurred

Calculation

soft start

0:Don’t care

1:Start

calculation

Calculation start trigger

000: Write to MACMA<7:0>

001: Write to MACMB<7:0>

010: Write to MACMOR<7:0>

011: Write to MACMOR<39:32>

1xx: Write of “1” to <MOPST>

Sign mode

0: Unsigned

1: Signed

Calculation mode

00: 64 + 32×32

01: 64 − 32×32

10: 32×32 − 64

11: Reserved

Note 1: <MOPST> is write-only and it is read as “0”.

Note 2: Writing “1xx” to <MSTTG2:0> and writing “1” to <MOPST> can be executed in the same write cycle.

Note 3: <MOVF> is fixed two system clocks (f

SYS

) after calculation is started.

MACCR

(1BFCH)

Prohibit

Read-modify

-write