TMP92CZ26A

92CZ26A-350

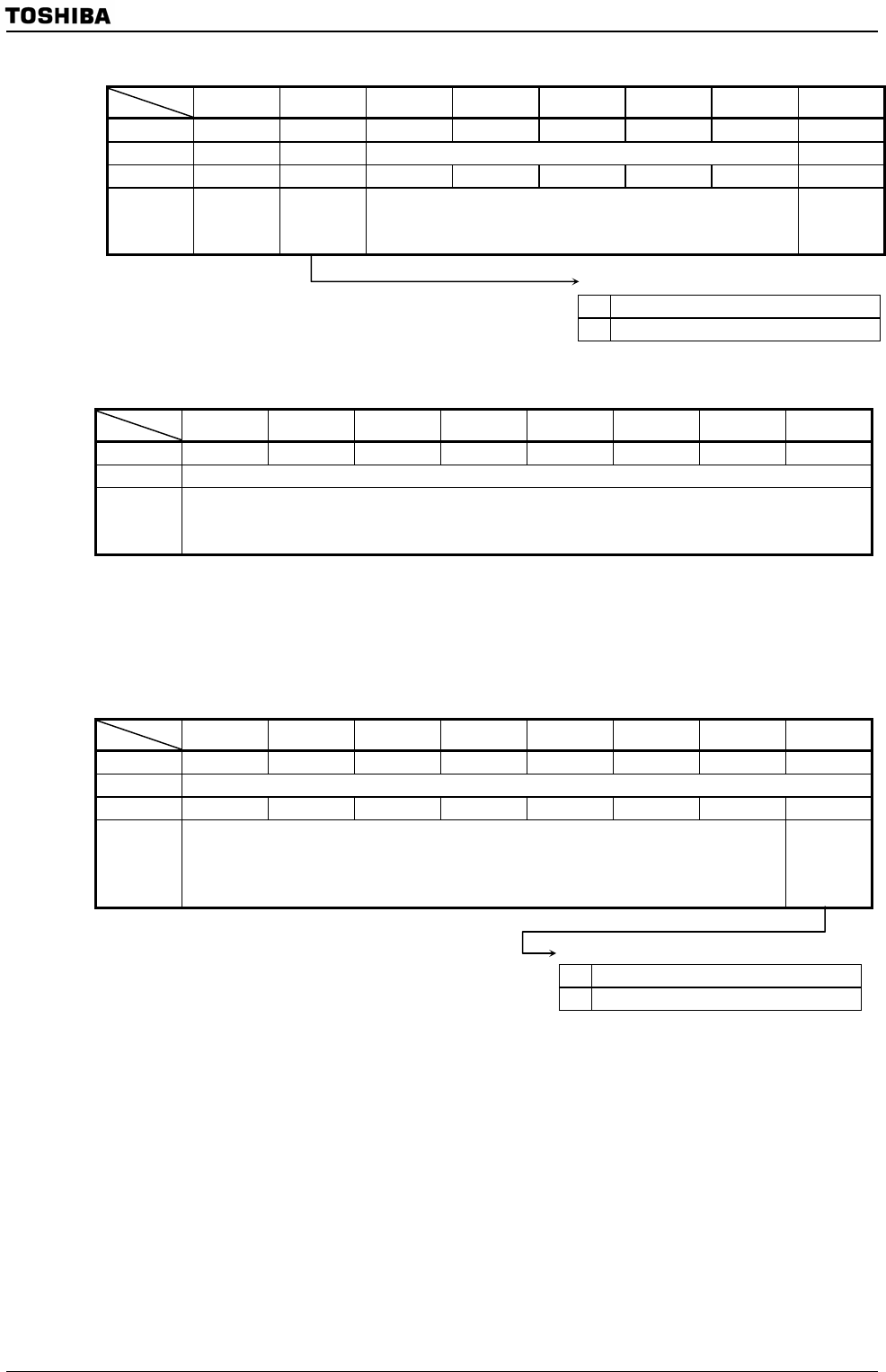

Serial Bus Interface Baud Rate Register 0

7 6 5 4 3 2 1 0

Bit symbol

−

I2SBI

− − − − − −

Read/Write W R/W R R/W

After reset 0 0 1 1 1 1 1 0

SBIBR0

(1244H)

Prohibit

Read-modify

-write

Function Always

read “0”

IDLE2

0: Stop

1: Run

Always read as “1” Always

write “0”.

Serial Bus Interface Data Buffer Register

7 6 5 4 3 2 1 0

Bit symbol DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 SBIDBR

(1241H)

Read/Write R (received)/W (transfer)

Prohibit

Read-modify

-write

After reset

Undefined

Note1: When writing transmitted data, start from the MSB (bit 7).Receiving data is placed from LSB(bit0).

Note2: SBIDBR can’t be read the written data because of it has buffer for writing and buffer for reading

individually.Therefore Read modify write instruction (e.g.“BIT” instruction ) is prohibitted.

Note3:Written data to SBIDBR is cleared by INTSBI signal.

I

2

C Bus Address Register

7 6 5 4 3 2 1 0

Bit symbol SA6 SA5 SA4 SA3 SA2 SA1 SA0 ALS I2CAR

(1242H)

Read/Write R/W

After reset 0 0 0 0 0 0 0 0 Prohibit

Read-modify

-write

Function Slave address selection for when device is operating as slave device Address

recognition

mode

specification

Address recognition mode specification

0 Slave address recognition

1 Non slave address recognition

Figure 3.15.7 Registers for the I

2

C bus mode

Operation during IDLE 2 mode

0 Stop

1 Operation