TMP92CZ26A

92CZ26A-220

3.10 SDRAM Controller (SDRAMC)

The TMP92CZ26A incorporates an SDRAM controller (SDRAMC) for accessing SDRAM that can

be used as data memory, program memory, or display memory.

The SDRAMC has the following features:

(1) Supported SDRAM

Data rate type : SDR (single data rate) type only

Memory capacity : 16 / 64 / 128 / 256 / 512 Mbits

Number of banks : 2 banks / 4 banks

Data bus width : 16 bits

Read burst length : 1 word / full page

Write mode : Single mode / Burst mode

(2) Supported initialization sequence commands

Precharge All command

Eight Auto Refresh commands

Mode Register Set command

(3) Access mode

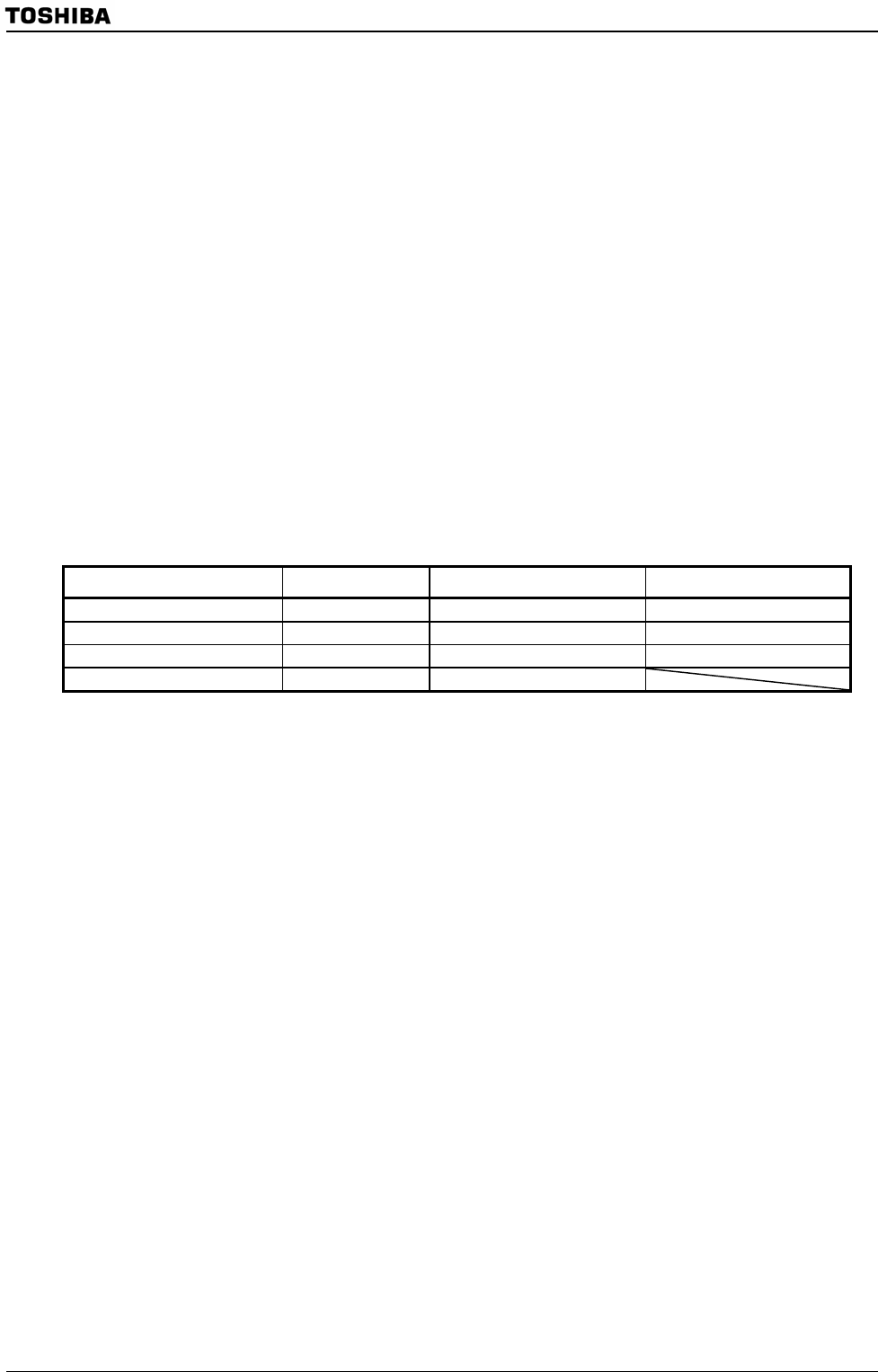

CPU Cycle HDMA Cycle LCDC Cycle

Burst length 1 word 1 word or full page selectable Full page

Addressing mode Sequential Sequential Sequential

CAS latency (clock) 2 2 2

Write mode Single Single or burst selectable

(4) Access cycles

CPU access cycles

Read cycle : 1 word, 4-3-3-3 states (minimum)

Write cycle : Single, 3-2-2-2 states (minimum)

Data size : 1 byte / 1 word / 1 long-word

HDMA access cycles

Read cycle : 1 word, 4-3-3-3 states / full page, 4-1-1-1 states (minimum)

Write cycle : Single, 3-2-2-2 states (minimum) / burst, 2-1-1-1 states (minimum)

Data size : 1 byte / 1 word / 1 long-word

LCDC access cycles

Read cycle : Full page, 4-1-1-1 states (minimum)

Data size : 1 word

(5) Auto generation of refresh cycles

• Auto Refresh is performed while the SDRAM is not being accessed.

• The Auto Refresh interval is programmable.

• The Self Refresh function is also supported.

Note: The SDRAM address area is determined by the CS1 or CS2 setting of the memory controller. However, the number of

bus cycle states is controlled by the SDRAMC.