TMP92CZ26A

92CZ26A-365

(5) Restart

Restart is used during data transfer between a master device and a slave device to

change the data transfer direction.

The following description explains how to restart when the TMP92CZ26A is in

Master Mode.

Clear SBICR2<MST, TRX, and BB> to 0 and set SBICR2<PIN> to 1 to release the

bus. The SDA line remains High and the SCL pin is released. Since a stop condition

has not been generated on the bus, other devices assume the bus to be in busy state.

And confirm SCL pin, that SCL pin is released and become bus-free state by

SBISR<BB> = “0” or signal level “1” of SCL pin in port mode. Check the <LRB> until it

becomes 1 to check that the SCL line on a bus is not pulled down to the low-level by

other devices. After confirming that the bus remains in a free state, generate a start

condition using the procedure described in (2).

In order to satisfy the set-up time requirements when restarting, take at least 4.7 μs of

waiting time by software from the time of restarting to confirm that the bus is free

until the time to generate the start condition.

7 6 5 4 3 2 1 0

SBICR2

←

0 0 0 1 1 0 0 0 Release the bus

if SBISR<BB> ≠ 0 Check if SCL pin is released.

Then

if SBISR<LRB> ≠ 1 Check if SCL pin of other device is “L” level.

Then

4.7 μs Wait

SBICR1

←

X X X 1 X X X X Set acknowledgement mode.

SBIDBR

←

X X X X X X X X Set the slave address and direction bit.

SBICR2

←

1 1 1 1 1 0 0 0 Generate start condition.

Note: X: Don’t care

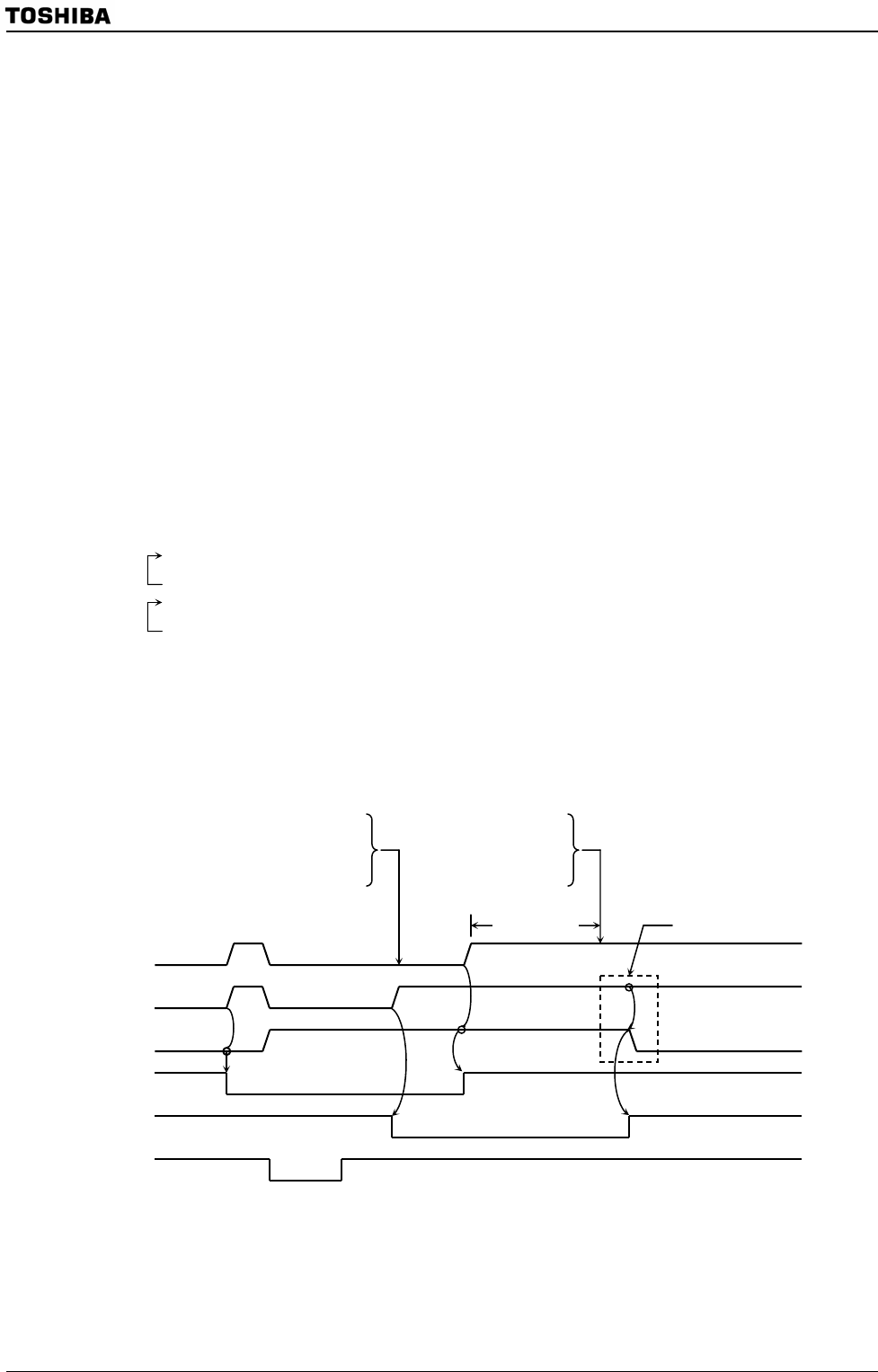

Figure 3.15.20 Timing chart for generate restart

Note: Don’t write <MST> = “0”, when <MST> = “0” condition. (Cannot be restarted)

Start condition

<LRB>

SCL line

Internal SCL

output

SDA line

<PIN>

4.7 μs (Min)

<BB>

“0” → <MST>

“0” → <TRX>

“0” → <BB>

“1” → <PIN>

“1” → <MST>

“1” → <TRX>

“1” → <BB>

“1” → <PIN>

9