TMP92CZ26A

92CZ26A-371

Mask registe

r

Writing “0” to flag registe

r

Flag registe

r

Interrupt source

(Set by rising edge)

ABCD

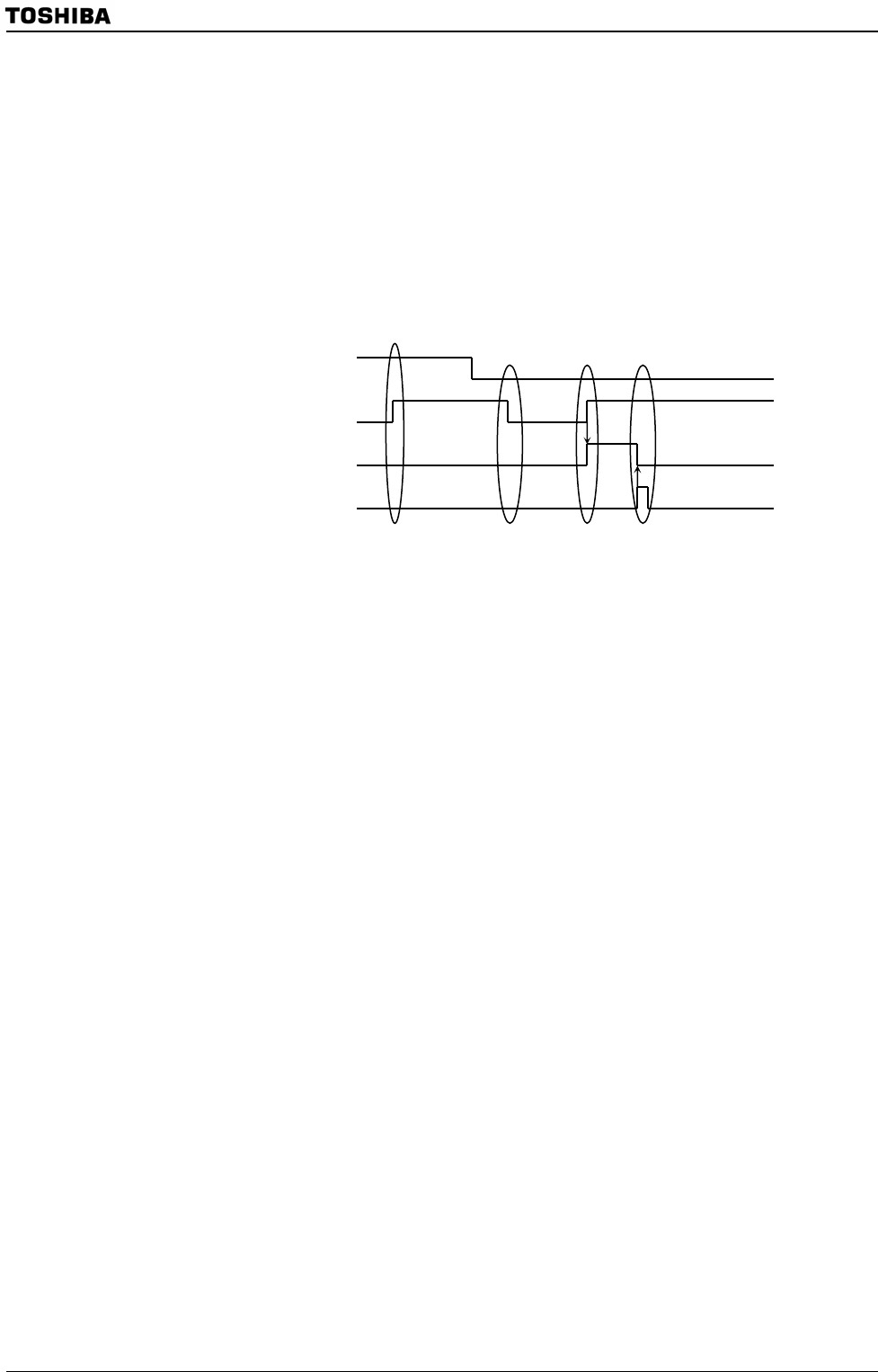

3.16.2.3 USBINTFRn, MRn Register

These SFRs control to generate INTUSB (only one interrupt to CPU) because the

UDC outputs 23 interrupt source.

The USBINTMRn are mask registers and the USBINTFRn are flag registers. In

the INTUSB routine, execute operations according to generated interrupt source after

checking USBINTFRn.

The below is the common specification for all MASK and FLAG registers.

(Common spec for all mask and flag registers.)

A: The flag register is not set because mask register = “1”.

B: The flag register is not set because interrupt souce changes “1” → “0”.

C: The flag register is set because mask register = “0” and interrupt souce changes “0” → “1”.

D: The flag register is reset to “0” by writing “0” to flag register.

Note 1: Both “INTUSB generated number” and “bit number which is set to flag register” are not always equal. In the

INTUSB interrupt routine, clear FLAG register (USBINTFRn) after checking it. The interrupt request flag, which

is occurred between jump to the INTUSB interrupt routine and read flag register (USBINTFRn), is kept in

interrupt controller.

Therefore, after returning from the interrupt routine, CPU jumps to INTUSB interrupt routine again. And

when read the flag register (USBINTFRn), none of the bits are set to “1”. For this case, special software is

needed in order not to finish as error routine.

Note 2: When USBINTMRn or USBINTFRn is written, disable INTUSB (write 00H to INTEUSB register) before it.