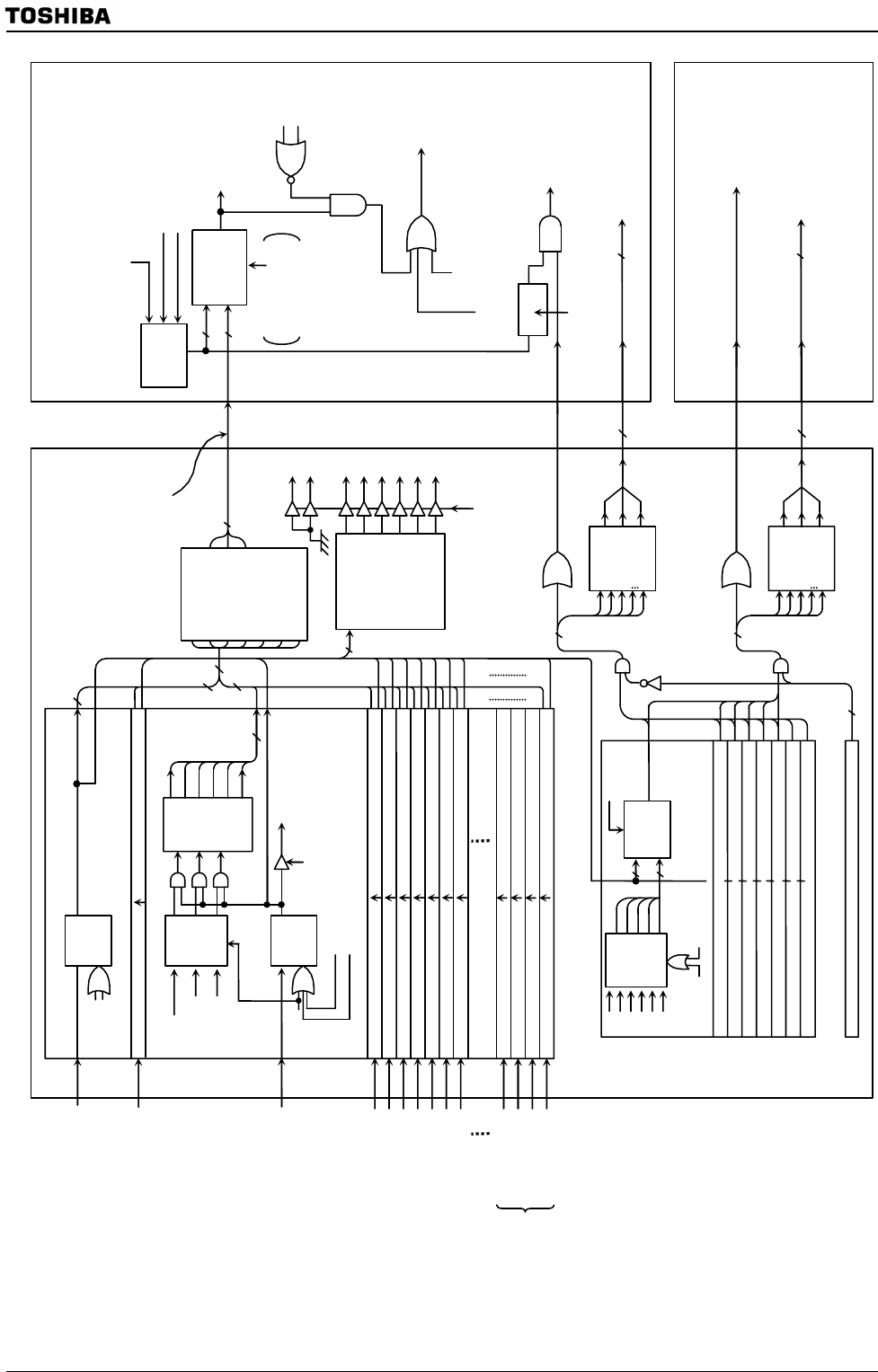

TMP92CZ26A

92CZ26A-77

Interrupt request

signal to CPU

IFF 7 then 0

Micro DMA/HDMA start vector setting register

INTTC4/INTDMA4

INTTC5/INTDMA5

INTTC6

INTTC7

V = E0H

V = E4H

V = E8H

V = ECH

Soft start

Micro

DMA/HDMA

counter 0

interrupt

6

INTTC0/

INTDMA0

During

IDLE1

52

3

3

3

6

1

7

3

3

8

6

51

8 input OR

INT0,1 to 4,INTKEY, INTRTC

INTALM

Micro DMA channel priority

encorder

Priority encorder

DMA0V

DMA1V

DMA2V

DMA3V

DMA4V

DMA5V

DMA6V

DMA7V

RESET

Interrupt request F/F

RESET

Decorder

Reset

Priority setting register

V = 20H

V = 24H

Interrupt controller CPU

S Q

R

V = 28H

V = 2CH

V = 30H

V = 34H

V = 38H

V = 3CH

V = 40H

V = 44H

D Q

CLR

Y1

Y2

Y3

Y4

Y5

Y6

A

B

C

Dn

Dn + 1

Dn + 2

Interrupt

request F/F

Interrupt vector read

Micro DMA acknowledge

Interrupt request F/F

Dn + 3

A

B

C

I

n

t

errup

t

vec

t

or

read

D2

D3

D4

D5

D6

D7

Selector

S Q

R

0

1

2

7

A

B

C

D0

D1

Interrupt vector

read

Interrupt mask F/F

Micro DMA request

HALT release

INTRQ2∼0 ≥ IFF

2∼0 then 1.

INTRQ2 to 0

IFF2 to 0

Interrupt

mask

detect

RESET

EI 1 to 7

DI

Interrupt request

signal

During

STOP

Micro DMA channel

specification

RESET

INTWD

INT0

INT1

INT2

INT3

INT4

INTALM

INTTA4

INTTA5

S

Interrupt vector

generator

Highest

priority

interrupt

level select

1

2

3

4

5

6

7

D5

D4

D3

D2

D1

D0

D Q

CLR

HDMA

3

6

6 input OR

HDMA channel priority

encorder

0

1

2

5

A

B

C

HDMA request

HDMA channel

Micro DMA/HDMA selection register

6

Figure 3.5.3 Block Diagram of Interrupt Controller