TMP92CZ26A

92CZ26A-345

3.15.2 Serial Bus Interface (SBI) Control

The following registers are used to control the serial bus interface and monitor the

operation status.

z Serial bus interface control register 0 (SBICR0)

z Serial bus interface control register 1 (SBICR1)

z Serial bus interface control register 2 (SBICR2)

z Serial bus interface data buffer register (SBIDBR)

z I

2

C bus address register (I2CAR)

z Serial bus interface status register (SBISR)

z Serial bus interface baud rate register 0 (SBIBR0)

3.15.3 The Data Formats in the I

2

C Bus Mode

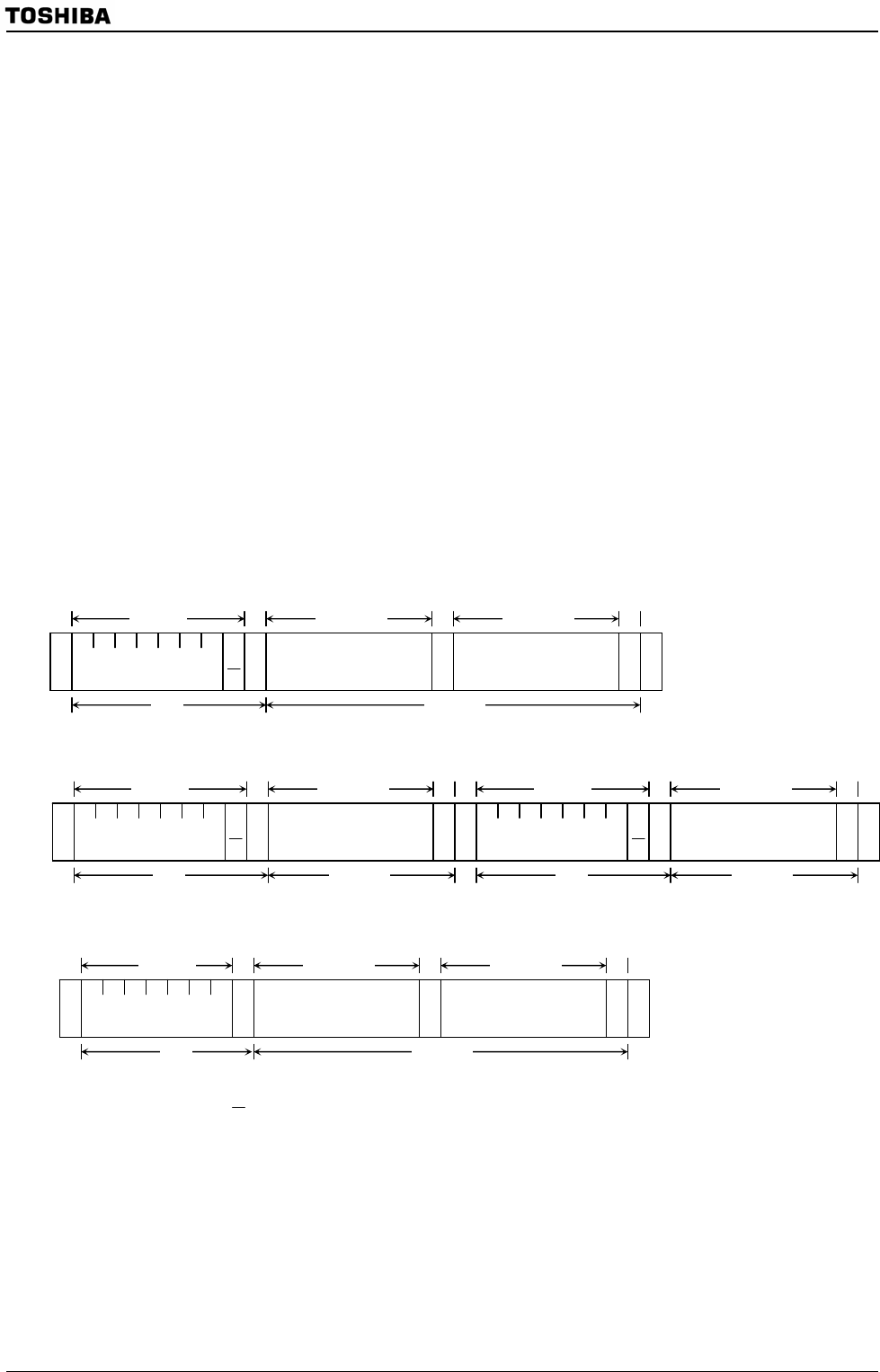

The data formats in the I

2

C bus mode is shown below.

(a) Addressing format

(b) Addressing format (with restart)

(c) Free data format (data transferred from master device to slave device)

Figure 3.15.2 Data format in the I

2

C bus mode

S Slave address

R

/

W

Data

A

C

K

A

C

K

Data

A

C

K

P

8 bits

1

1 to 8 bits

1

1 to 8 bits

1

1 1 or more

S Slave address

R

/

W

Data

A

C

K

A

C

K

S Slave address

R

/

W

Data

A

C

K

A

C

K

P

8 bits

1

1 to 8 bits

1

8 bits

1

1 to 8 bits

1

1 1 or more 1 1 or more

S Data Data

A

C

K

A

C

K

Data

A

C

K

P

8 bits

1

1 to 8 bits

1

1 to 8 bits

1

1 1 or more

S: Start condition

R/

W : Direction bit

ACK: Acknowledge bit

P: Stop condition