TMP92CZ26A

92CZ26A-275

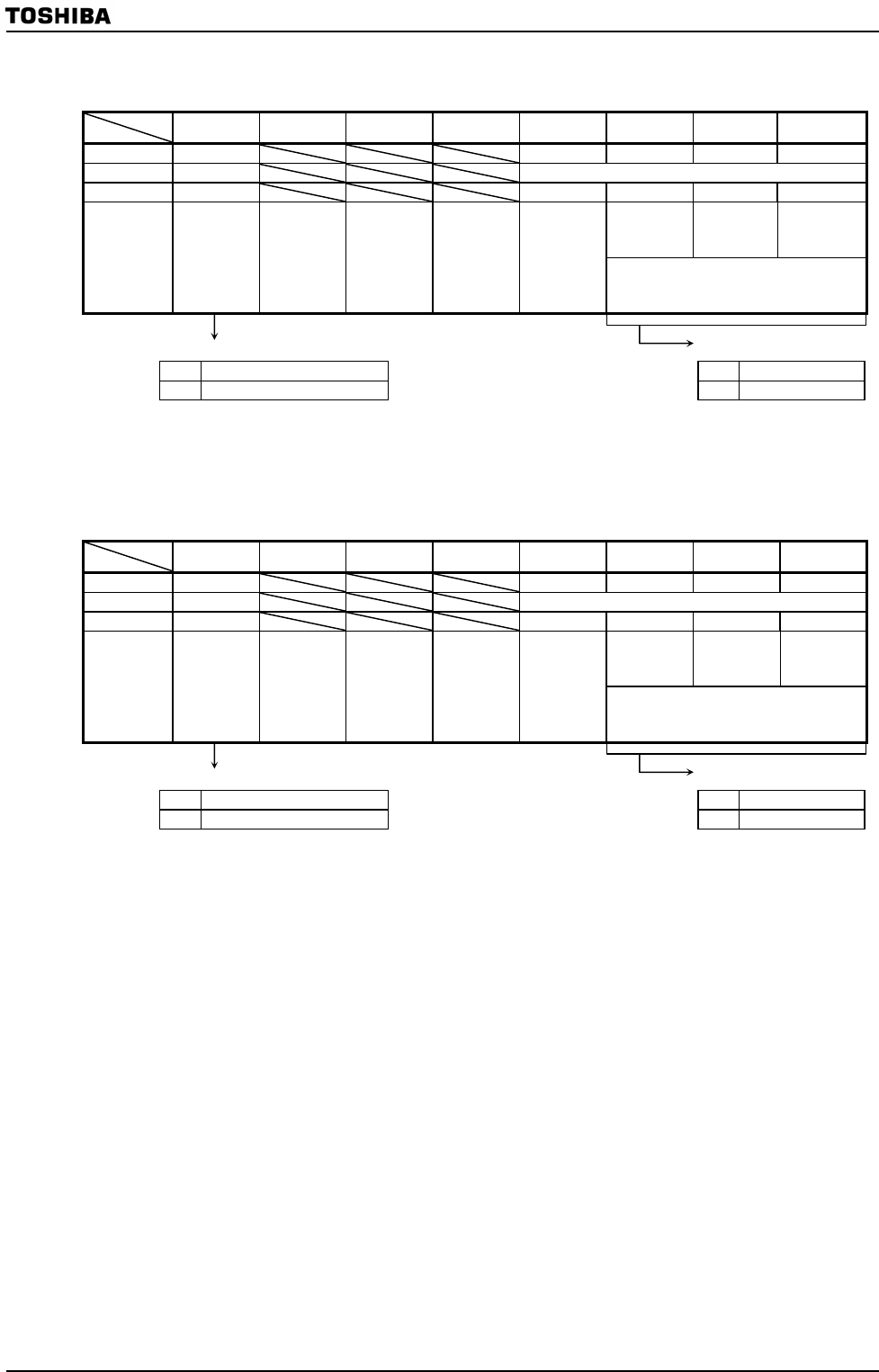

TMRA45 RUN Register

7 6 5 4 3 2 1 0

Bit symbol TA4RDE I2TA45 TA45PRUN TA5RUN TA4RUN

Read/Write R/W R/W

After Reset 0 0 0 0 0

TMRA45

prescaler

Up counter

(UC5)

Up counter

(UC4)

Function

Double

buffer

0: Disable

1: Enable

In IDLE2

mode

0: Stop

1: Operate

0: Stop and clear

1: Run (Count up)

Note: The values of bits 4 to 6 of TA45RUN are “1” when read.

TMRA67RUN Register

7 6 5 4 3 2 1 0

Bit symbol TA6RDE I2TA67 TA67PRUN TA7RUN TA6RUN

Read/Write R/W R/W

After Reset 0 0 0 0 0

TMRA67

prescaler

Up counter

(UC7)

Up counter

(UC6)

Function

Double

buffer

0: Disable

1: Enable

In IDLE2

mode

0: Stop

1: Operate

0: Stop and clear

1: Run (Count up)

Note: The values of bits 4 to 6 of TA67RUN are “1” when read.

Figure 3.12.7 Register for TMRA (2)

TA45RUN

(1110H)

TA4REG double buffer control

0 Disable

1 Enable

Count control

0 Stop and clear

1 Run (Count up)

TA67RUN

(1118H)

TA6REG double buffer control

0 Disable

1 enable

Count control

0 Stop and clear

1 Run (Count up)