TMP92CZ26A

92CZ26A-407

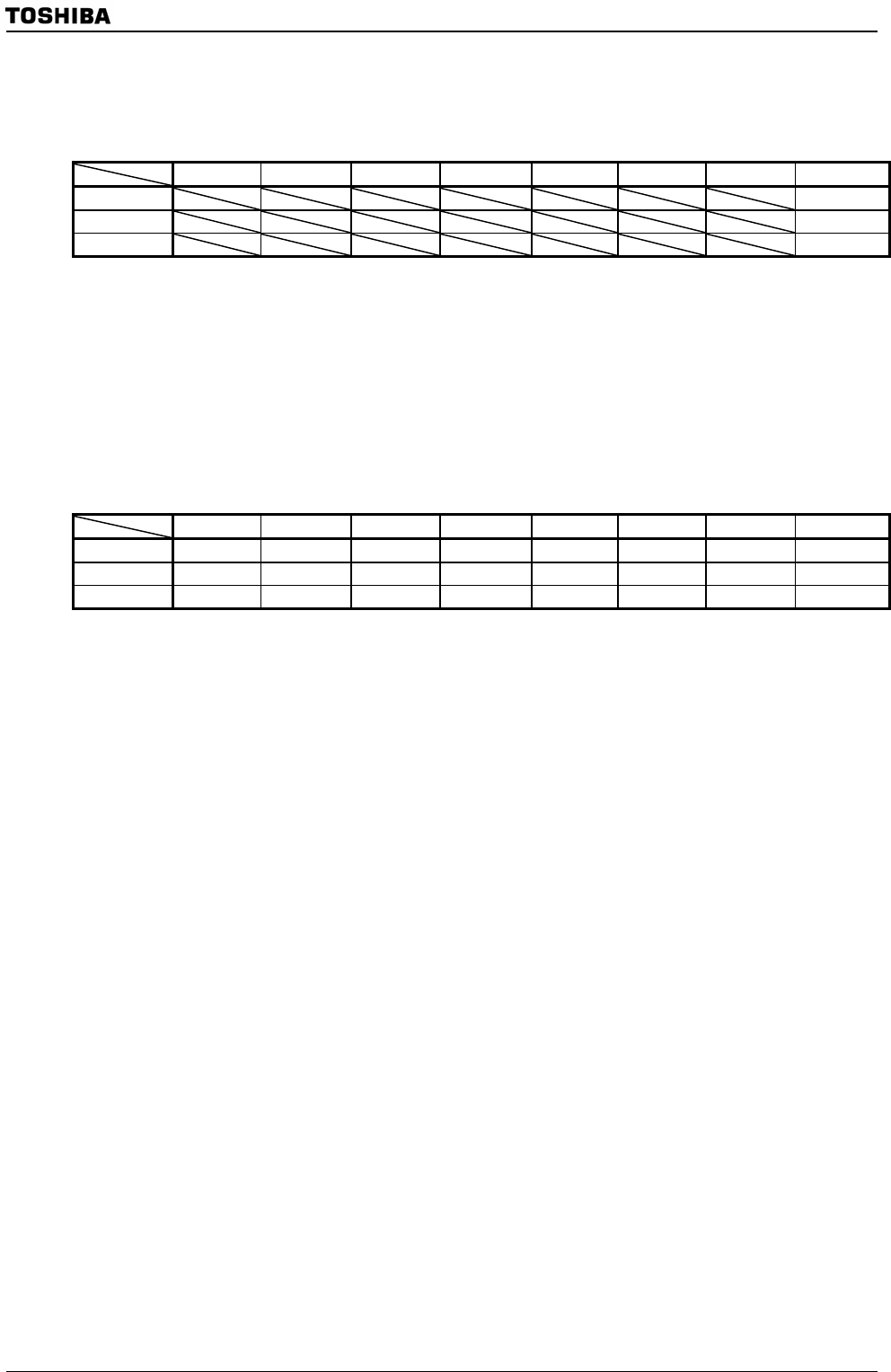

3.16.3.28 Set Descriptor STALL Register

This register sets whether returns STALL automatically in data stage or status

stage for Set Descriptor Request.

7 6 5 4 3 2 1 0

bit Symbol

S_D_STALL

Read/Write W

After reset 0

Bit0: S_D_STALL

0: Software control (Default)

1: Automatically STALL

3.16.3.29 Descriptor RAM Register

This register is used for store descriptor to RAM. Size of descriptor is 384 bytes.

However, when storing descriptor, write according to descriptor RAM structure

sample.

7 6 5 4 3 2 1 0

bit Symbol

D7 D6 D5 D4 D3 D2 D1 D0

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

After reset Undefined Undefined Undefined Undefined Undefined Undefined Undefined Undefined

This register can Read/Write only following timing; before detect USB_RESET,

during processing SET_DESCRIPTOR request.

SET_DESCRIPTOR request processes from INT_SETUP assert until access EOP

register.

If there is rewriting request of descriptor in SET_DESCRIPTOR, process request

following sequence.

1) Read descriptor that is transferred by SET_DESCRIPTOR requests every packet.

2) When reading descriptor number of last packet finished, write all descriptors to

RAM for descriptor.

3) When writing finished, execute INIT_DESCRIPTOR of COMMAND register.

4) When all process finished, access EOP register, and finish status stage.

5) When INT_STAS is received, it shows normal finish of status stage.

If USB_RESET is detected, it starts reading automatically. Therefore, when it

connect to host, executing of INIT_DESCRIPTOR command is not needed.

Set Descriptor STALL

(07E8H)

~

Descriptor RAM

(0500H)

(067FH)