TMP92CZ26A

92CZ26A-419

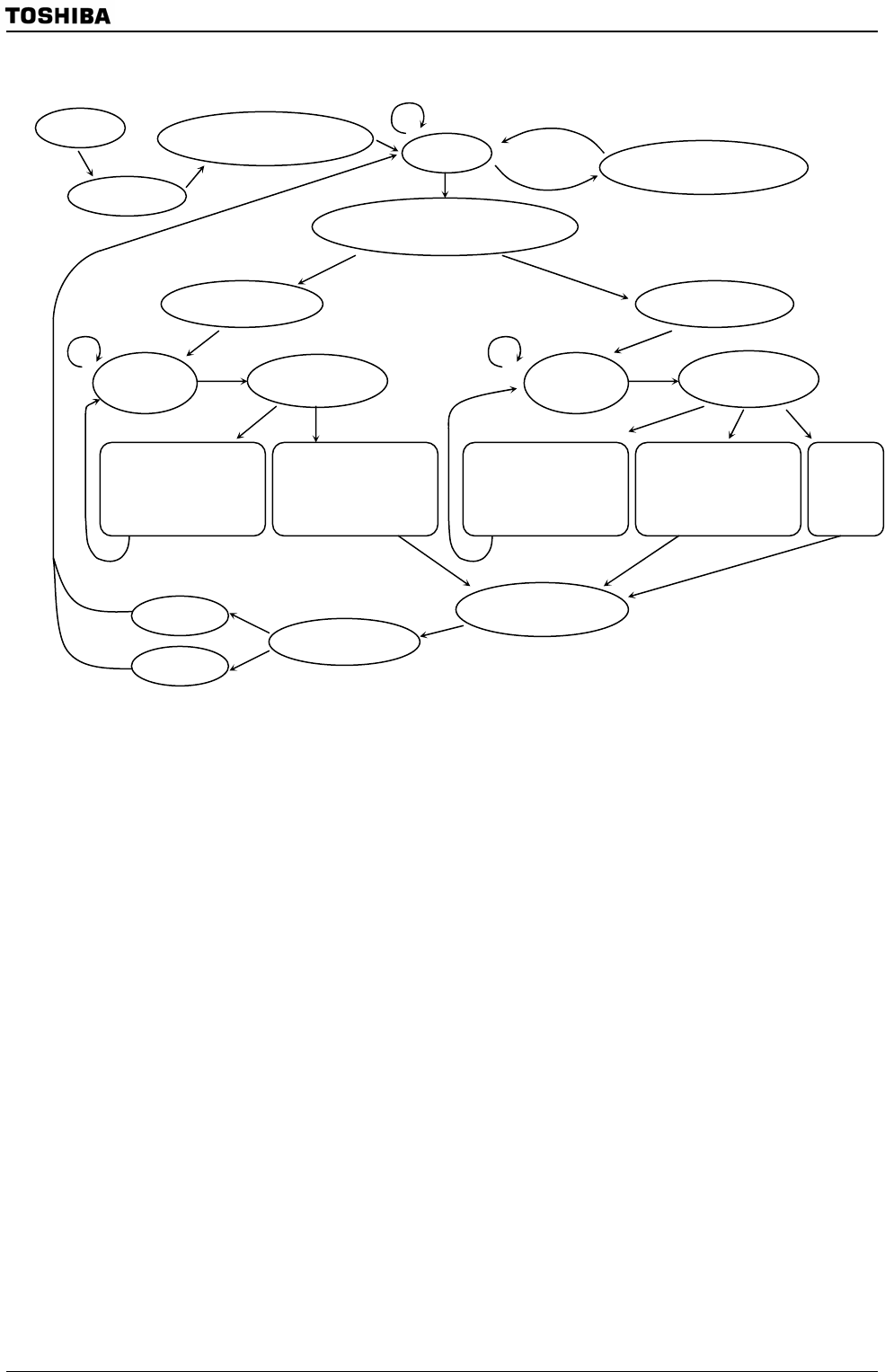

Below is control flow in UDC watch from application.

Figure 3.16.6 Control Flow in UDC Watch from Application

Note 1: There is not special case in this flow such as overlap receive SETUP packet.

Please refer to chaptor 4.5.2.3.

Note 2: This flow shows various request. However, transaction can be divided every each interrupt.

Start up

Enumeration

Setting each EP mode

in Set_Config (Interface)

IDLE

Judge request RD

Access to SetupReceived register

Get_Vendor_Request

transaction

Set_Vendor_Request

transaction

Check

DATASET

register

Transmit

judgement

Total_Length

Total ≥ payload

WR number of payload

to EP0_FIFO register

Total = Total − payload

Total < payload

WR number of rest data

to EP0_FIFO

Total = 0

EP0 bit = 1

EP0 bit = 0

Receive

except

INT_STATUS

Receive

INT_STAS

Status finish

transacrion in UDC

Check

DATASET

register

Receive

judgement

Total_Length

Total > payload

RD number of payload

from EP0_FIFO register

Total = Total − payload

Total ≤ payload

RD number of rest data

from EP0_FIFO

Total = 0

Total

=

0

Not

transaction

Total = 0

EP0 bit

=

0

EP0 bit = 1

Control RD transfe

r

Control WR transfe

r

Standard request

Printerclass request

WR “0” only EP0 bit0 o

f

EOP register

Abnormal

finish

Normal

finish