TMP92CZ26A

92CZ26A-374

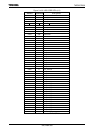

7 6 5 4 3 2 1 0

bit Symbol INT_SETUP INT_EP0 INT_STAS INT_STASN INT_EP1N INT_EP2N INT_EP3N

Read/Write R/W R/W R/W R/W R/W R/W R/W

After reset 0 0 0 0 0 0 0

Function When read 0: Not generate interrupt

1: Generate interrupt

When write 0: Clear flag

1: −

Note: Above interrupt can release Halt state from IDLE2 mode. (IDLE1 and STOP mode can not be released.)

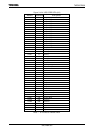

• INT_SETUP (Bit7)

This is a flag for INT_SETUP (setup - interrupt).

This is set to “1” when the UDC receive request that S/W (software) control

is needed from USB host.

By S/W (INT_SETUP routine), at first, read device request of 8-bytes from

UDC and execute operation according to each request.

• INT_EP0 (Bit6)

This is a flag for INT_EP0 (received data of the data phase for Control

transfer type - interrupt).

This is set to “1” when the UDC receive data of the data phase for Control

transfer type. At the Control write transfer, data reading from FIFO is needed

if this interrupt occur. At the Control read transfer, transmission data writing

to FIFO is needed if this interrupts occurred.

By host may don’t assert “ACK” of last packet in the data stage. In that case,

this interrupt cannot be generated. So, ignore this interrupt of after last

packet data was written in the data stage because the transmission data

number is specified by the host, or it depends on the capacity of the device.

• INT_STAS (Bit5)

This is a flag for INT_STAS (status stage end - interrupt).

This is set to “1” when the status stage end.

If this interrupt is generated, it means that request ended normally.

If this interrupt is not generated and INT_SETUP is generated,

EP0_STATUS <STAGE_ERR> is set to “1” and it means that request didn’t

end normally.

USBINTFR4

(07F3H)

Prohibit

to read

modify

write