TMP92CZ26A

92CZ26A-233

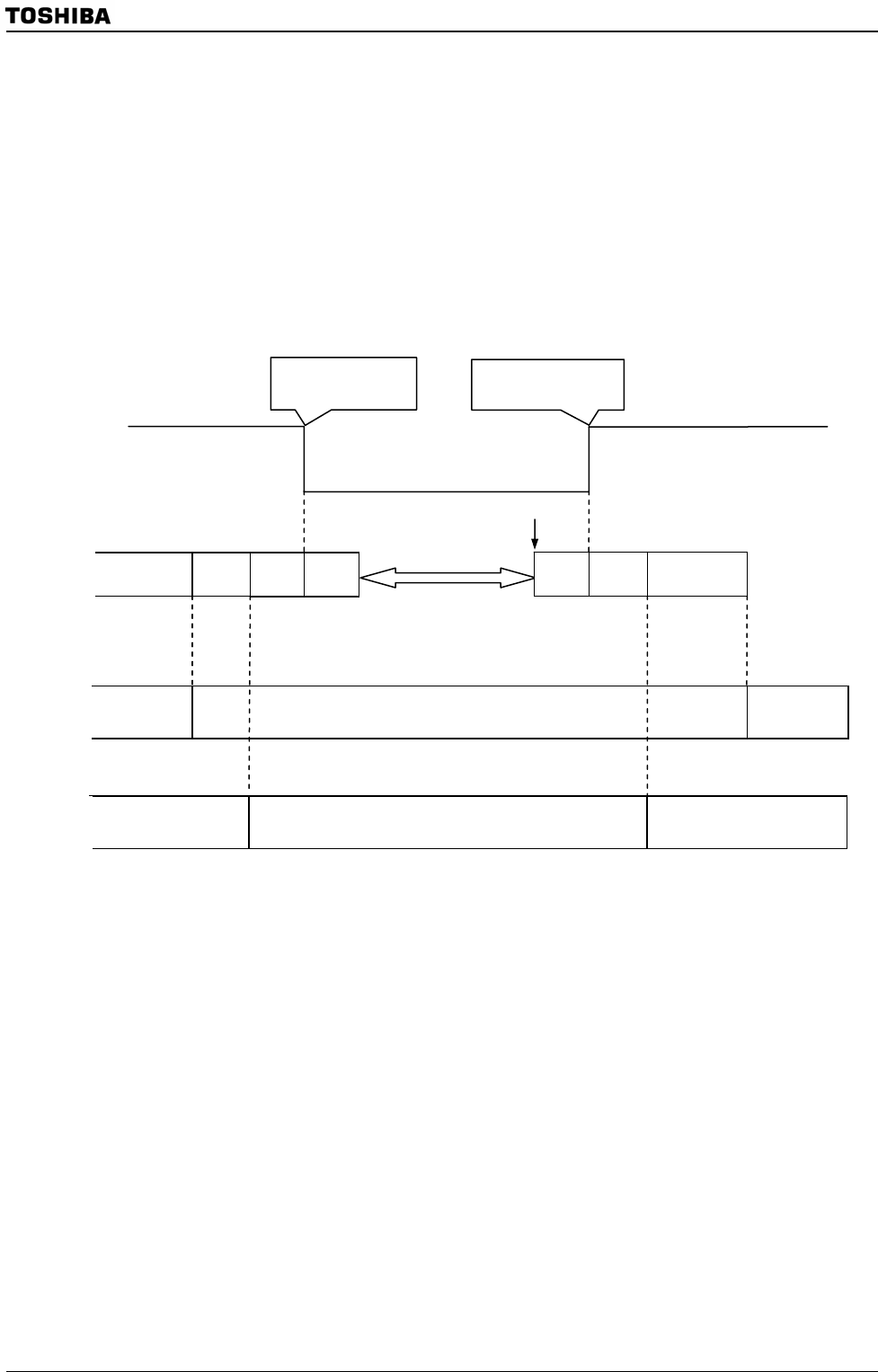

The Self Refresh state can be exited by the Self Refresh Exit command. The Self Refresh

Exit command is executed when SDCMM<SCMM2:0> is set to “110”. It is also executed

automatically in synchronization with HALT mode release. In either of these two cases,

Auto Refresh is performed immediately after the Self Refresh state is exited. Then, Auto

Refresh is executed at specified intervals. Exiting the Self Refresh state clears

SDCMM<SCMM2:0> to “000”.

Setting SDRCR<SSAE> to “0” disables automatic execution of the Self Refresh Exit

command in synchronization with HALT release. The auto exit function should also be

disabled in cases where the SDRAM operation requirements cannot be met as the operation

clock frequency is reduced by clock gear down, as shown in

Figure3.10.8.

Figure3.10.8 Execution Flow for Executing HALT Instruction after Clock Gear Down

HALT mode

Gear down

SR

ENTRY

CLK

change

HALT

Interrupt

Auto Exit

disable

Self Refresh

Gear up

f

SYS

CPU

SDRAM controller

internal state

Auto-EXIT

disable

Auto-EXIT

enable

SR

EXIT

CLK

change

Auto Exit

enable

SDRAM state

Auto Refresh

Auto Exit

enable

Auto Refresh

60MHz

625 KHz (10MHz/16)