TMP92CZ26A

92CZ26A-349

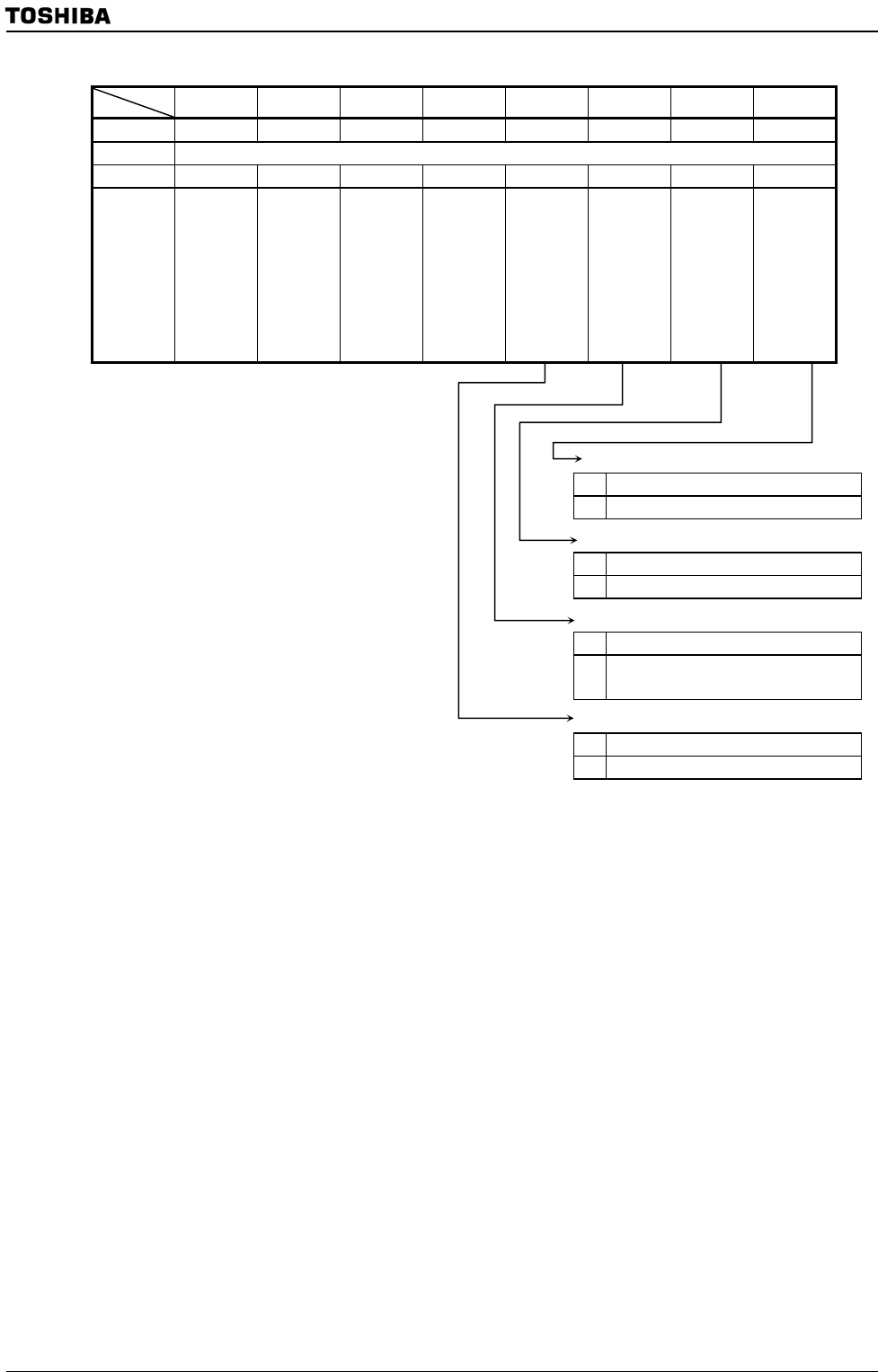

Serial Bus Interface Status Register

7 6 5 4 3 2 1 0

Bit symbol MST TRX BB PIN AL AAS AD0 LRB SBISR

(1243H)

Read/Write R

After reset 0 0 0 1 0 0 0 0

Prohibit

Read-modif

y-write

Function Master/

Slave status

monitor

0:Slave

1:Master

Transmitter/

Receiver

status

monitor

0:Receiver

1:Tranmitter

I

2

C bus

status

monitor

0:Free

1:Busy

INTSBI

interrupt

request

monitor

0: Interrupt

requested

1: Interrupt

canceled

Arbitration

lost

detection

monitor

0: −

1: Detected

Slave

address

match

detection

monitor

0: Undetected

1: Detected

GENERAL

CALL

detection

monitor

0: Undetected

1: Detected

Last

received bit

monitor

0: 0

1: 1

Last received bit monitor

0 Last received bit was 0

1 Last received bit was 1

GENERAL CALL detection monitor

0

Undetected

1 GENERAL CALL detected

Slave address match detection monitor

0

Slave address don’t match or Undetected

1

Slave address match or GENERAL

CALL detected

Arbitration lost detection monitor

0

−

1 Arbitration lost

Note1: Writing in this register functions as SBICR2.

Note2: The initialdata SBISR<PIN> is “1” if SBI operation is enable (SBICR0<SBIEN>=“1”). If SBI operation is disable

(SBICR0<SBIEN>=“0”), the initialdata of SBISR<PIN> is “0”.

Figure 3.15.6 Registers for the I

2

C bus mode