TMP92CZ26A

92CZ26A-22

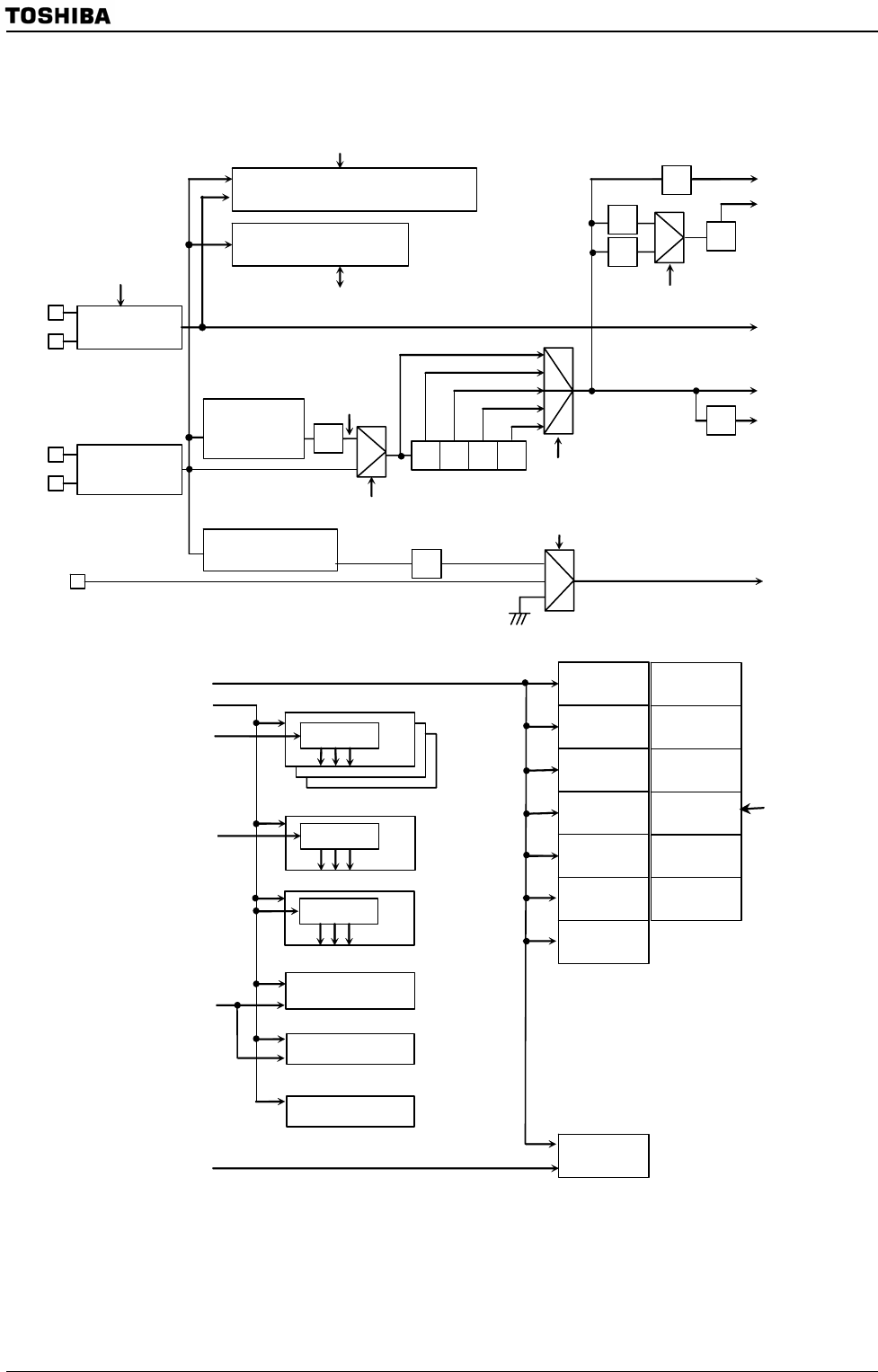

3.3.1 Block diagram of system clock

Clock gear

SYSCR0<PRCK>

fs

f

OSCH

Low frequency

Oscillator circuit

XT1

XT2

SYSCR0<XTEN >

Warming up timer

(High/Low frequency oscillator circuit)

SYSCR0<WUEF>

SYSCR2<WUPTM1:0>

X1

X2

÷2 ÷16÷4

fc/16

fc/8

fc/4

fc/2

fc

PLLCR0<FCSEL>

SYSCR1<GEAR2:0>

÷2

f

SYS

÷2

φT0TM

R

fs

φT0

High frequency

Oscillator circuit

÷8

÷2

f

IO

Lock up timer

(PLL)

PLLCR1<PLLON>,

PLLCR0<LUPFG>

÷8

Clock Doubler1

(PLL1)× 24

f

USB

SYSCR0<USBCLK1:0>

÷5

f

PLLUSB

X1USB

TMRA0:7,TMRB0:1

f

SYS

CPU

RAM

Interrupt

Controller

I/O ports

Prescaler

φT0TMR

SIO0

RTC

fs

Prescaler

MLD/ALM

SDRAMC

f

io

LCDC

Memory

Controlle

r

NAND-Flash

Controlle

r

I

2

S

TSI

SPIC

SBI

Prescaler

DMAC

MAC

f

USB

USB

ADC

÷2

f

PLL

Clock Doubler0

(PLL0)

×

(

12 or16

)

f

OSCH4

÷4

φT0

Figure 3.3.2 Block Diagram of System clock