TMP92CZ26A

92CZ26A-171

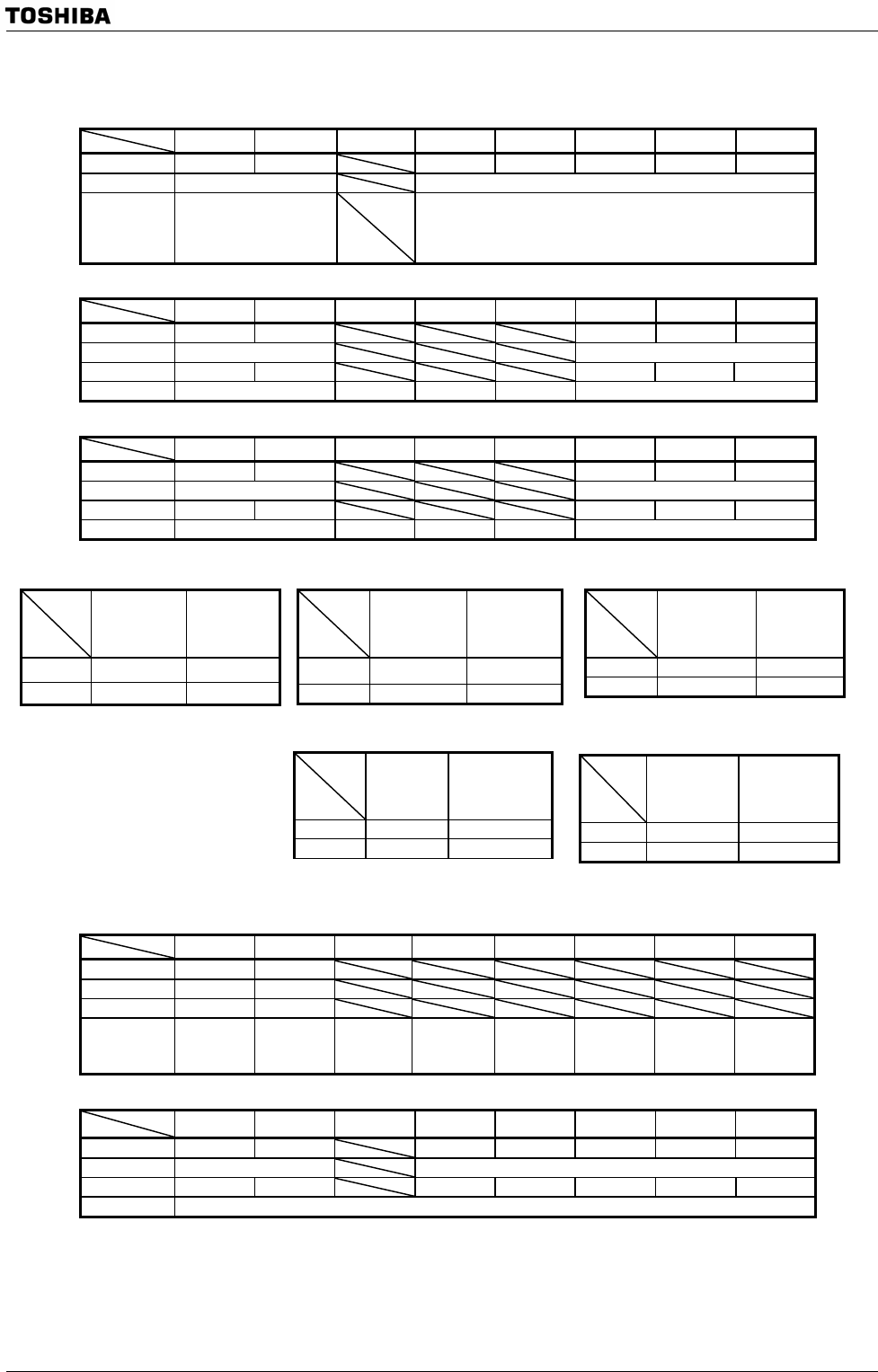

Port V register

7 6 5 4 3 2 1 0

bit Symbol PV7 PV6 PV4 PV3 PV2 PV1 PV0

Read/Write R/W R/W

After reset

Data from external port

(Output latch register is

cleared to “0”)

Data from external port

(Output latch register is cleared to “0”)

Port V control register

7 6 5 4 3 2 1 0

bit Symbol PV7C PV6C PV2C PV1C PV0C

Read/Write W

After reset 0 0 0 0 0

Function 0: Input 1: Output 0: Input 1: Output

Port V function register

7 6 5 4 3 2 1 0

bit Symbol PV7F PV6F PV2F PV1F PV0F

Read/Write W W

After reset 0 0 0 0 0

Function Refer to following table Refer to following table

Port V function register 2

7 6 5 4 3 2 1 0

bit Symbol PV7F2 PV6F2

Read/Write W W

After reset 0 0

Function

0:CMOS

1:Open

-drain

0:CMOS

1:Open

-drain

Port V drive register

7 6 5 4 3 2 1 0

bit Symbol PV7D PV6D PV4D PV3D PV2D PV1D PV0D

Read/Write R/W R/W

After reset 1 1 1 1 1 1 1

Function Input/Output buffer drive register for standby mode

Figure 3.7.60 Register for Port V

PVFC

(00ABH)

PV

(00A8H)

PVCR

(00AAH)

PVDR

(009DH)

PVFC2

(00A9H)

<PV0C>

<PV0F>

0 1

0 Input port Output port

1 Reserved SCLK0 output

Note: SCLK0 is only output.

PV0 setting

<PV1C>

<PV1F>

0 1

0 Input port Output port

1 Reserved Reserved

PV1 setting

<PV2C>

<PV2F>

0 1

0 Input port Output port

1

Reserved Reserved

PV2 setting

<PV6C>

<PV6F>

0 1

0 Input port Output port

1 Reserved SDA I/O

PV6 setting

<PV7C>

<PV7F>

0 1

0 Input port Output port

1 Reserved SCL I/O

PV7 setting

Note: Read-Modify-Write is prohibited for the registers PVCR, PVFC and PVFC2.