TMP92CZ26A

92CZ26A-373

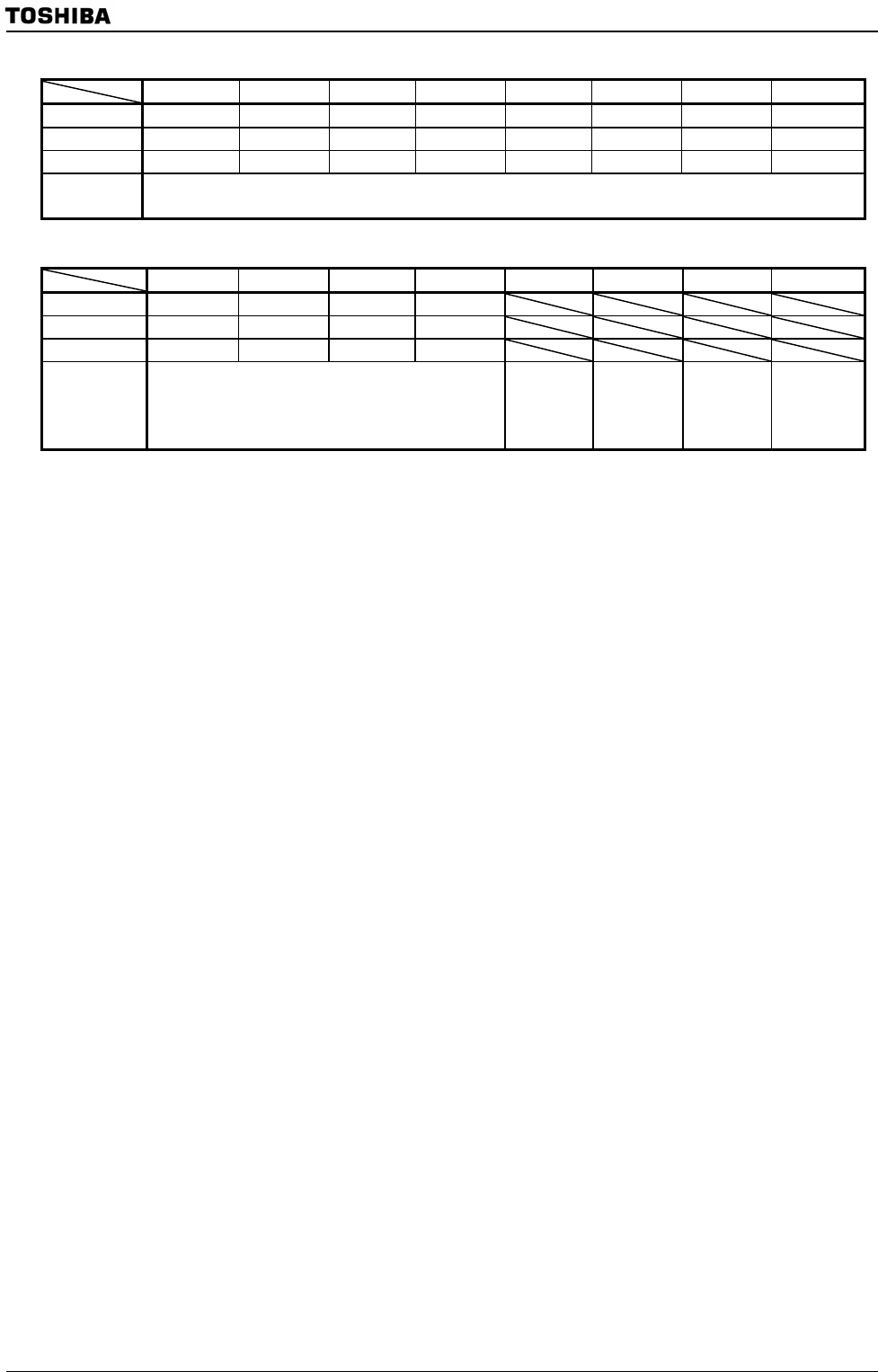

7 6 5 4 3 2 1 0

bit Symbol EP1_FULL_A EP1_Empty_A EP1_FULL_B EP1_Empty_B EP2_FULL_A EP2_Empty_A EP2_FULL_B EP2_Empty_B

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

After reset 0 0 0 0 0 0 0 0

Function When read 0: Not generate interrupt

1: Generate interrupt

When write 0: Clear flag

1: −

Note: Above interrupt can release Halt state from IDLE2 mode. (IDLE1 and STOP mode can not be released.)

7 6 5 4 3 2 1 0

bit Symbol EP3_FULL_A EP3_Empty_A EP3_FULL_B EP3_Empty_B

Read/Write R/W R/W R/W R/W

After reset 0 0 0 0

Function When read 0: Not generate interrupt

1: Generate interrupt

When write 0: Clear flag

1: −

Note: Above interrupt can release Halt state from IDLE2 mode. (IDLE1 and STOP mode can not be released.)

• EPx_FULL_A/B:

(When transmitting)

This is set to “1” when CPU full write data to FIFO_A/B.

(When receiving)

This is set to “1” when UDC full receive data to FIFO_A/B.

• EPx_Empty_A/B:

(When transmitting)

This is set to “1” when FIFO become empty after transmission.

(When receiving)

This is set to “1” when FIFO become empty after CPU read all data from FIFO.

Note: The flag of EPx_FULL_A/B and EPx_Empty_A/B are not status flag. Therefore, check DATASET

register if the FIFO-status is needed.

USBINTFR2

(07F1H)

Prohibit

to read

modify

write

USBINTFR3

(07F2H)

Prohibit

to read

modify

write