TMP92CZ26A

92CZ26A-636

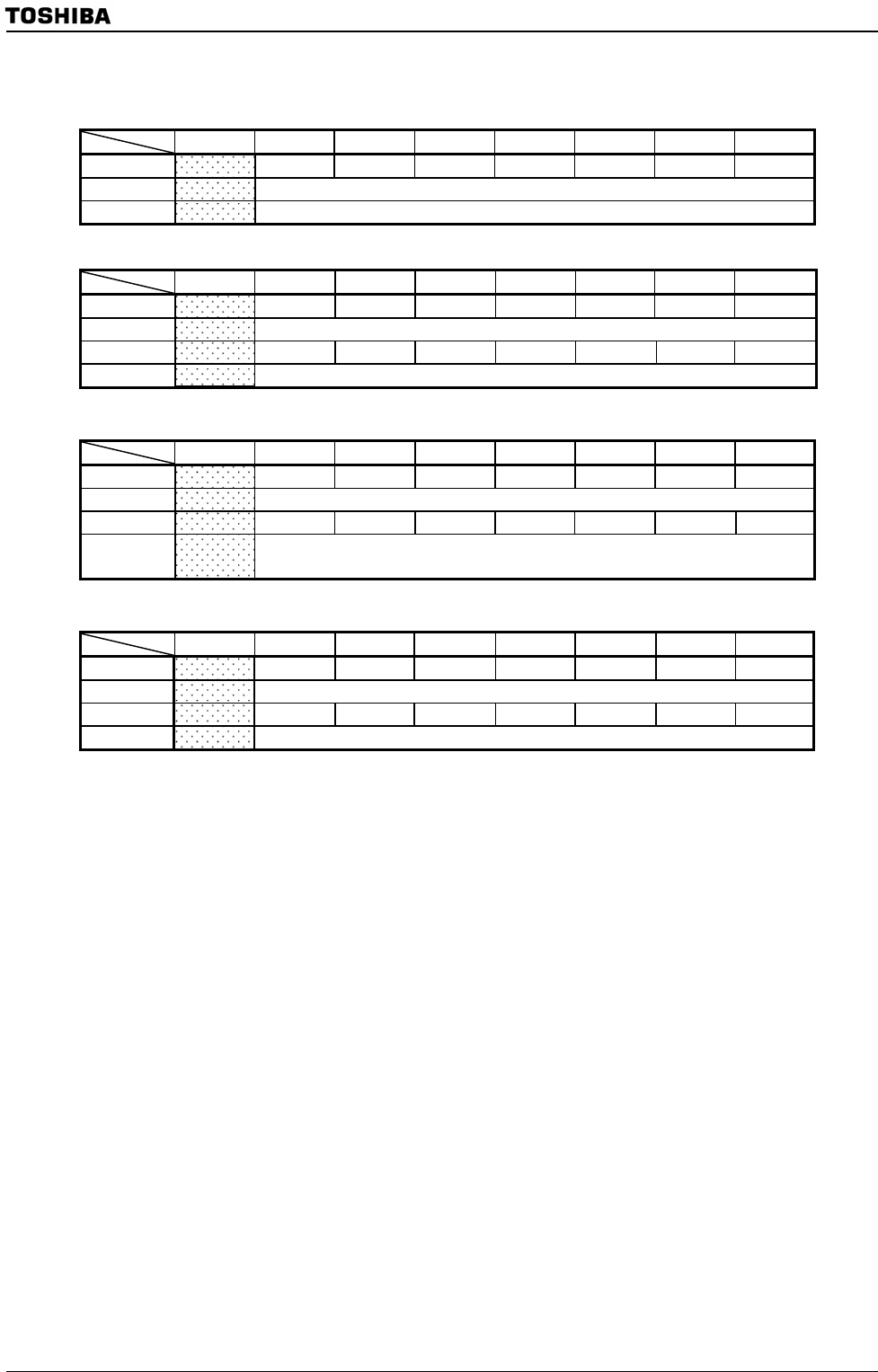

Port U Register

7 6 5 4 3 2 1 0

Bit Symbol PU7 PU6 PU5 PU4 PU3 PU2 PU1 PU0

Read/Write R/W

After reset External pin data (Output latch is reset to “0”.)

Port U Control Register

7 6 5 4 3 2 1 0

Bit Symbol PU7C PU6C PU5C PU4C PU3C PU2C PU1C PU0C

Read/Write W

After reset 0 0 0 0 0 0 0 0

Function 0: Input 1: Output

Port U Function Register

7 6 5 4 3 2 1 0

Bit Symbol PU7F PU6F PU5F PU4F PU3F PU2F PU1F PU0F

Read/Write W

After reset 0 0 0 0 0 0 0 0

Function

0: Port 1: Data bus for LCDC (LD23 to LD16)

Note: When LD23 to LD16 are used, set <PUnC> to “1”.

Port U Drive Register

7 6 5 4 3 2 1 0

Bit Symbol PU7D PU6D PU5D PU4D PU3D PU2D PU1D PU0D

Read/Write R/W

After reset 1 1 1 1 1 1 1 1

Function Input/output buffer drive register for standby mode

Note: Although it is possible to write to shaded bits, writing to these bits has no effect (the DSU communication function is

given a higher priority).

PUFC

(00A7H)

PUCR

(00A6H)

PUDR

(009CH)

PU

(00A4H)