TMP92CZ26A

92CZ26A-550

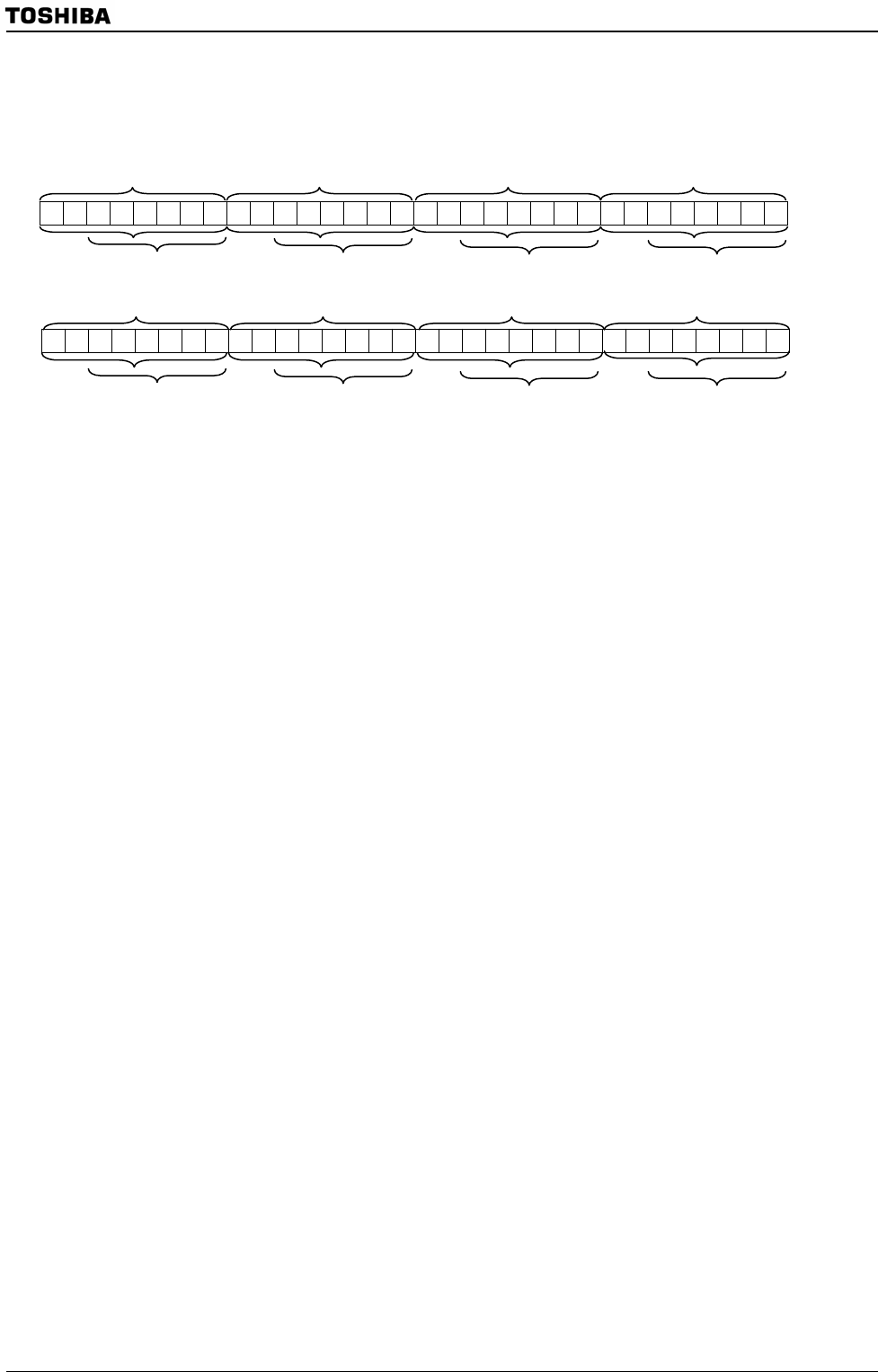

TFT 262144-/16777216-color (24 bpp: R: 8 bits, G: 8 bits, B: 8 bits)

Display Memory

24-bit TFT 18-bit TFT

LD18 0(R0) → 24(R1)

LD19 1(R0) → 25(R1)

LD0 2(R0) → 26(R1) LD0 2(R0) 26(R1)

LD1 3(R0) → 27(R1) LD1 3(R0) 27(R1)

LD2 4(R0) → 28(R1) LD2 4(R0) 28(R1)

LD3 5(R0) → 29(R1) LD3 5(R0) 29(R1)

LD4 6(R0) → 30(R1) LD4 6(R0) 30(R1)

LD5 7(R0) → 31(R1) LD5 7(R0) 31(R1)

LD20 8(G0) → 32(G1)

LD21 9(G0) → 33(G1)

LD6 10(G0) → 34(G1) LD6 10(G0) → 34(G1)

LD7 11(G0) → 35(G1) LD7 11(G0)

→ 35(G1)

LD8 12(G0) → 36(G1) LD8 12(G0) → 36(G1)

LD9 13(G0) → 37(G1) LD9 13(G0) → 37(G1)

LD10 14(G0) → 38(G1) LD10 14(G0) → 38(G1)

LD11 15(G0) → 39(G1) LD11 15(G0) → 39(G1)

LD22 16(B0) → 40(B1)

LD23 17(B0) → 41(B1)

LD12 18(B0) → 42(B1) LD12 18(B0) → 42(B1)

LD13 19(B0) → 43(B1) LD13 19(B0) → 43(B1)

LD14 20(B0) → 44(B1) LD14 20(B0) → 44(B1)

LD15 21(B0) → 45(B1) LD15 21(B0) → 45(B1)

LD16 22(B0) → 46(B1) LD16 22(B0) → 46(B1)

LD17 23(B0) → 47(B1) LD17 23(B0) →

47(B1)

Note: The display RAM data format for 18 bpp is the same as that for 24 bpp. When 18 bpp is used, the least significant

bit should be disabled by port setting.

Figure 3.19.10 Memory Map Image and Data Output in TFT 262144-/16777216-Color Mode

Address 4 Address 5 Address 6 Address 7

LSB MSB

D0 D31

32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63

G2 B2 R3 G3

Address 0 Address 1 Address 2 Address 3

LSB MSB

D0 D31

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0 G0 B0 R1