TMP92CZ26A

92CZ26A-199

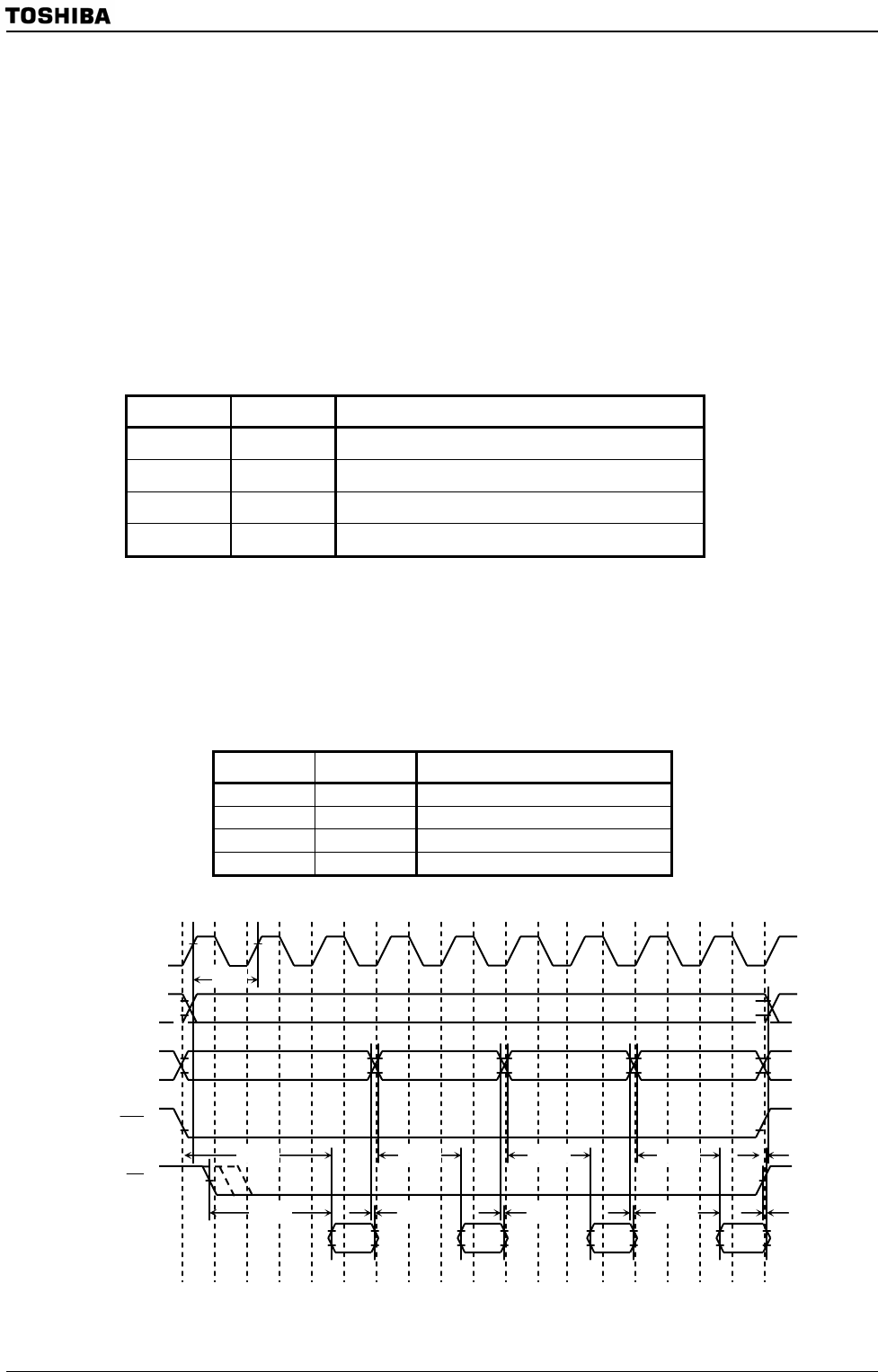

3.8.4 ROM Page mode Access Control

This section describes ROM page mode accessing and how to set registers. ROM page mode

is set by PMEMCR.

(1) Operation and how to set the registers

TMP92CZ26A supports ROM access with the page mode. The ROM access with the page

mode is specified only in CS2.

Setting PMEMCR<OPGE> to “1” sets the memory access of CS2 to ROM page mode access.

The number of read cycles is set by the PMEMCR<OPWR1:0>.

PMEMCR<OPWR1:0>

<OPWR1> <OPWR0> Number of Cycle in a Page

0 0 1 state (n-1-1-1 mode) (n ≥ 2)

0 1 2 state (n-2-2-2 mode) (n ≥ 3)

1 0 3 state (n-3-3-3 mode) (n ≥ 4)

1 1 4 state (n-4-4-4 mode) (n ≥ 5)

Note: Set the number of waits “n” to the control register (BnCSL) in each block address area.

The page size (the number of bytes) of ROM in the CPU size is set to PMEMCR<PR1:0>.

When data is read out until a border of the set page, the controller completes the page reading

operation. The start data of the next page is read in the normal cycle. The following data is set

to page read again.

PMEMCR<PR1:0>

<PR1> <PR0> ROM Page Size

0 0 64 bytes

0 1 32 bytes

1 0 16 bytes (Default)

1 1 8 bytes

Figure 3.8.5 Page mode access Timing

A0~A1

2CS

RD

D0~D15

+0

+

1

+

2 +3

Input

Data

Input

Data

Input

Data

Input

Data

t

AD3

t

AD2

t

AD2

t

AD2

t

H

A

t

HR

t

RD3

t

H

A

t

H

A

t

H

A

t

CYC

SDCLK

A2~A23