TMP92CZ26A

92CZ26A-221

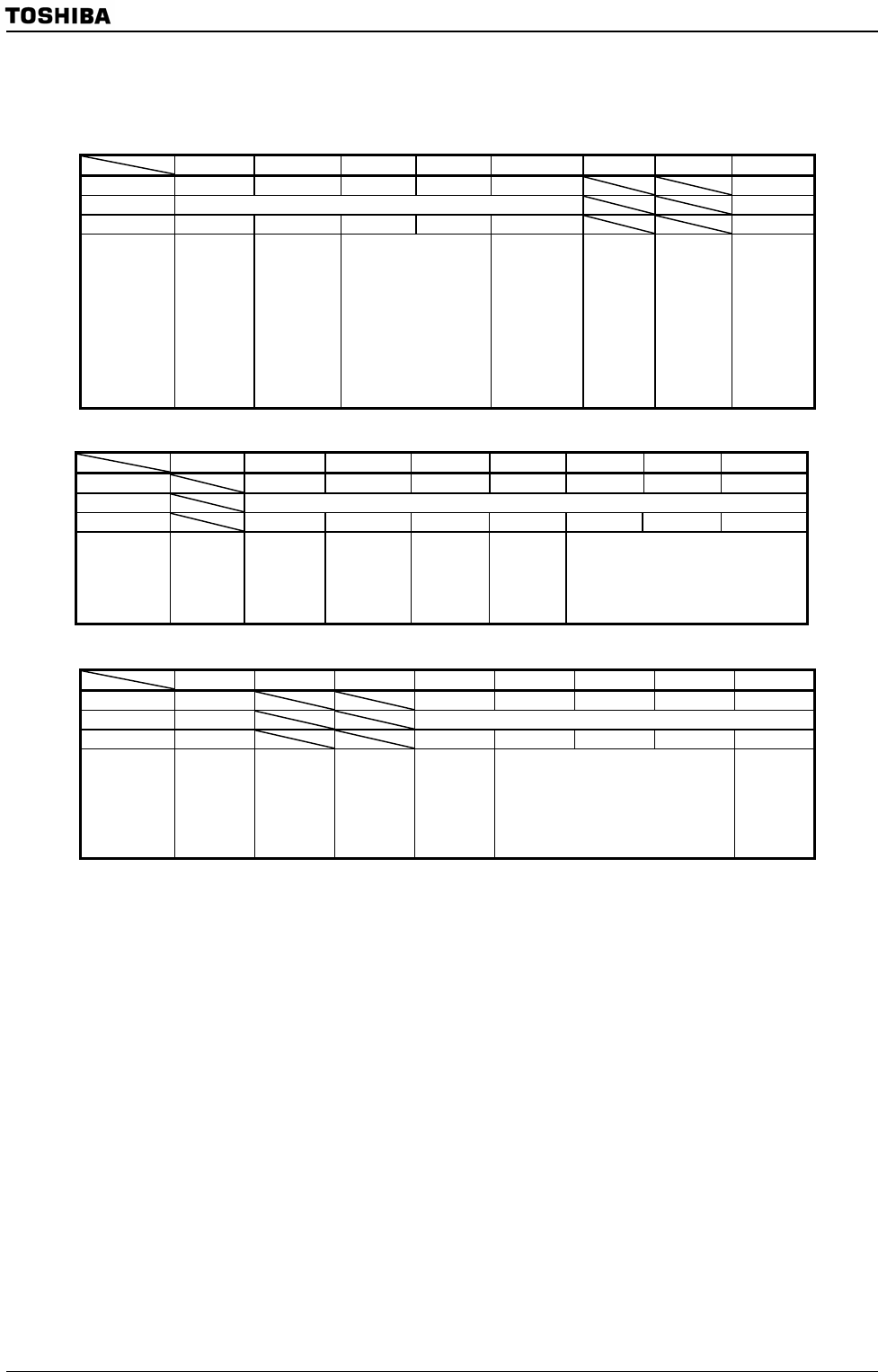

3.10.1 Control Registers

The SDRAMC has the following control registers.

SDRAM Access Control Register

7 6 5 4 3 2 1 0

Bit symbol SRDS – SMUXW1 SMUXW0 SPRE SMAC

Read/Write R/W R/W

After reset 1 0 0 0 0 0

Function

Read data

shift

function

0: Disable

1: Enable

Always

write “0”

Address multiplex type

00: Type A (A9- )

01: Type B (A10- )

10: Type C (A11- )

11: Reserved

Read/Write

commands

0: Without

auto pre-

charge

1: With auto

precharge

SDRAM

controller

0: Disable

1: Enable

SDRAM Command Interval Setting Register

7 6 5 4 3 2 1 0

Bit symbol STMRD STWR STRP STRCD STRC2 STRC1 STRC0

Read/Write R/W

After reset 1 1 1 1 1 0 0

Function

TMRD

0: 1 CLK

1: 2 CLK

TWR

0: 1 CLK

1: 2 CLK

TRP

0: 1 CLK

1: 2 CLK

TRCD

0: 1 CLK

1: 2 CLK

TRC

000: 1 CLK 100: 5 CLK

001: 2 CLK 101: 6 CLK

010: 3 CLK 110: 7 CLK

011: 4 CLK 111: 8 CLK

SDRAM Refresh Control Register

7 6 5 4 3 2 1 0

Bit symbol − SSAE SRS2 SRS1 SRS0 SRC

Read/Write R/W R/W

After reset 0 1 0 0 0 0

Function

Always

write “0”

Self

Refresh

auto exit

function

0:Disable

1:Enable

Refresh interval

000: 47 states 100: 468 states

001: 78 states 101: 624 states

010: 156 states 110: 936 states

011: 312 states 111: 1248 states

Auto

Refresh

0:Disable

1:Enable

SDACR

(0250H)

SDRCR

(0252H)

SDCISR

(0251H)