TMP92CZ26A

92CZ26A-312

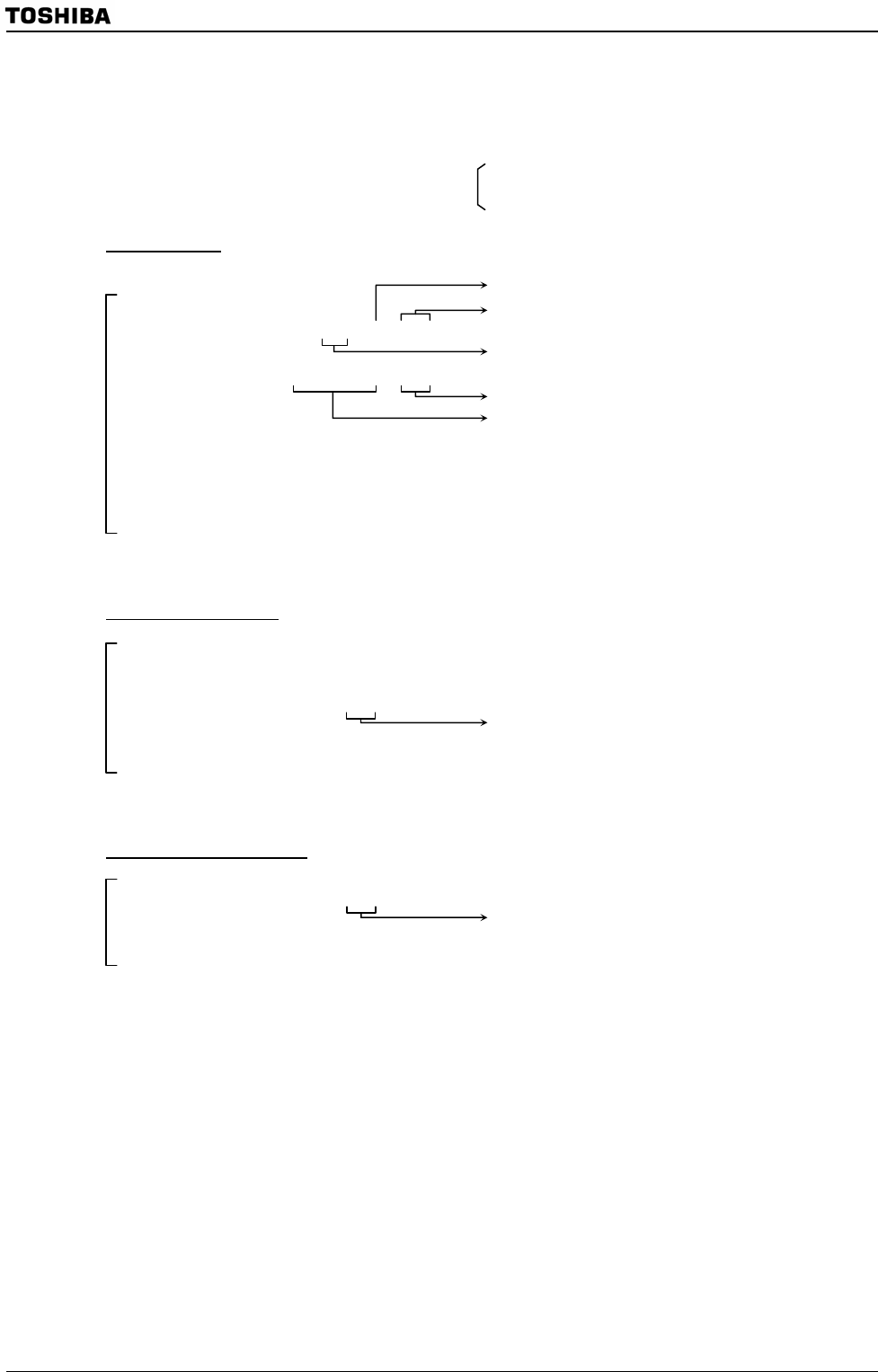

Example: To output 2ms one-shot pulse with 3ms delay to the external trigger pulse to

TB0IN0pin

*Clock state

System clock : f

SYS

Prescaler clock : f

SYS

/4

Main setting

Free-running

Count with φT1

TB0MOD

←

X X 1 0 1 0 0 1

Load to TB0CP0H/L at the rising edge of TB0IN0

TB0FFCR

←

X X 0 0 0 0 1 0

Clear TB0FF0 to “0”

Disable TB0FF0 inversion

PPFC

←

– 1 – – – – – X

Select PP6 as TB0OUT0 pin (port setting)

INTE56

←

X 1 0 0 X – – –

Enable INT6

INTETB0

←

X 0 0 0 X 0 0 0 Disable INTTB00, INTTB01

TB0RUN

←

– 0 X X – 1 X 1 Start TMRB0

Setting in INT6 routine

TB0RG0

←

TB0CP0 + 3ms/φT1

TB0RG1

←

TB0RG0 + 2ms/φT1

TB0FFCR

←

X X – – 1 1 – –

Enable TB0FF0 inversion when the up counter value

matches TB0RG0H/L or TB0RG1H/L

INTETB0

←

X 1 0 0 X 0 0 0 Enable INTTB01

Setting in INTTB01 routine

TB0FFCR

←

X X – – 0 0 – –

Disable TB0FF0 inversion when the up counter value

matches TB0RG0H/L or TB0RG1H/L

INTETB0

←

X 0 0 0 X 0 0 0 Disable INTTB01

X: Don't care, −: No change

When delay time is unnecessary, invert timer flip-flop TB0FF0 when the up counter

value is loaded into capture register (TB0CP0H/L), and set the TB0CP0H/L value (c)

plus the one –shot pulse width (p) to TB0RG1H/L when the interrupt INT6 occurs.

The TB0FF0 inversion should be enabled when the up counter (UC10) value matched

TB0RG1H/L, and disabled when generating the interrupt INTTB01.